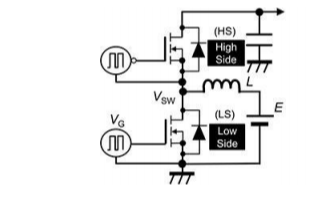

下面给出的电路图是在桥式结构中使用 SiC MOSFET 时最简单的同步式 boost 电路。该电路中使用的 SiC MOSFET 的高边(HS)和低边(LS)是交替导通的,为了防止 HS 和 LS 同时导通,设置了两个 SiC MOSFET 均为 OFF 的死区时间。右下方的波形表示其门极信号(VG)时序。

2020-12-07 22:44

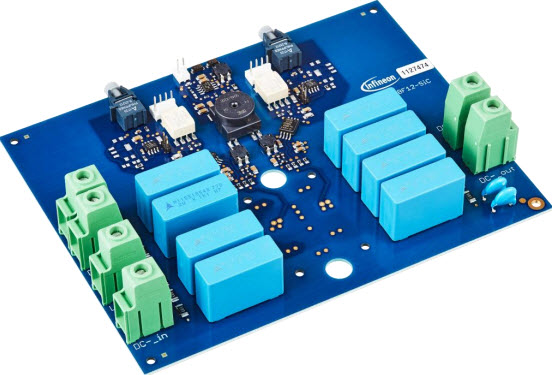

View the reference design for EVAL-PS-E1BF12-SIC. http://www.elecfans.com/soft/ has thousands of reference designs to help bring your project to life.

2021-07-12 20:04

SiC功率MOSFET内部晶胞单元的结构,主要有二种:平面结构和沟槽结构。平面SiCMOSFET的结构,如图1所示。这种结构的特点是工艺简单,单元的一致性较好,雪崩能量比较高。但是,这种结构的中间

2023-06-19 16:39

CREE第二代SiCMOSFET驱动电路原理图及PCB板设计电路原理图光耦隔离电路和功率放大电路原理图隔离电源电路原理图PCB layout第一层layout第二层layout(负电层)第三层

2021-11-08 14:51

CREE第二代SiCMOSFET驱动电路原理图及PCB板设计电路原理图光耦隔离电路和功率放大电路原理图隔离电源电路原理图PCB layout第一层layout第二层layout(负电层)第三层

2021-11-15 07:26

在 400VAC 50/60Hz 并网连接时的最大输出功率为 10kW/10KVA工作功率因数范围为 0.7 滞后至 0.7 超前基于高压 (1200V) SiCMosFET 的全桥逆变器,峰值效率高

2018-10-29 10:23

已成为限制SiCMOSFET发展的主要因素。理论和实验均表明.高密度的界面态电荷和非理想平面造成的表面粗糙是导致SiCMOS器件表面 迁移率低的主要因素。用单电子MonteCarlo方法对6H—SiC

2017-06-16 10:37