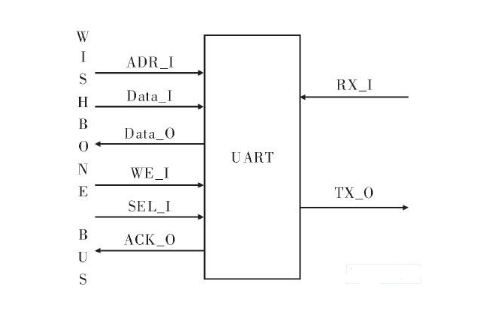

本文介绍的基于Wishbone总线的UART IP核的设计方法,通过验证表明了各项功能达到预期要求,为IP核接口的标准化设计提供了依据。此外,该IP核代码全部采用模块化的Verilog-HDL语言编写,

2011-06-10 11:47

注意3.30:在总线周期期间置位ERR_I信号,会立即结束该周期,意味着从机通知主机在该周期期间发生了错误。当从机逻辑电路检测到错误,便会置位ERR_I信号。例如,如果从机使用了奇偶校检,当发生错误时,从机便会通过ERR_I做出反应。

2018-07-12 08:38

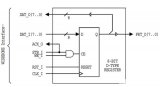

在以上介绍的三种总线中,CoreConnect虽免费不过需要IBM 公司许可,ARM 没有明确的正式说法,可能也会免费,而Wishbone 是绝对免费的。三种总线都是同步的总线,使用时钟上升沿驱图7 8-bit SLAVE输出端口动和采样信号。

2018-08-11 09:14

Am29LV160D是一种仅需采用3.0V电源进行读写的闪存。该器件提供了70ns、90ns、120ns读取时间,无需高速微处理器插入等待状态进行速度匹配。为了消除总线竞争,芯片引入了片选使能(CE#),写使能(WE#)和输出使能(OE#)控制端口。芯片采用分块结构,非常适用于要求高密度的代码或数据存储的低功耗系统。

2018-07-17 15:58

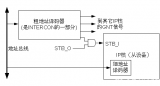

Wishbone部分地址译码的实现如图26所示。对于图中所示IP核,我们假设其只有4个地址,对应4组寄存器。地址译码器首先译码出其地址并给出选择信号,该选择信号与共享总线的STB_O相与输入到IP核的STB_I。而地址总线的最低2位被直接连接到IP核,IP核再根据这两位译码出当前操作选中的是具体哪个寄存器。

2018-08-05 08:44

支持用户定义的标签。这些标签可以用于为地址、数据总线提供额外的信息如奇偶校验,为总线周期提供额外的信息如中断向量、缓存控制操作的类型等。Wishbone规范只定义标签的时序,而标签的具体含义用户可自行定义。支持用户定义的标签是Wishbone规范区别与其他片上总线

2018-07-06 08:07

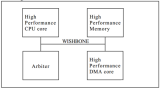

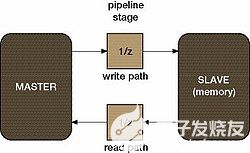

前文曾经指出,Wishbone总线规范是"轻量级(Lightweight)"规范,它实现起来非常简单紧凑,接口需要的互联逻辑非常少。这里给出一个Wishbone从设备的一个例子,如图21所示。该从

2018-07-31 09:11

在时钟上升沿1,主设备将DAT_I()采样完成整个突发读操作,同时主设备将新地址信号放到地址总线ADR_O()上,将新数据信号放到数据总线DAT_O()上,将WE_O置为高表示写操作,CTI_O()置为3’b111表示本次写操作只进行一次。由于从设备根据CTI_O()为3’b111知道整个突发读操作结束,而不了解主设备将发起写操作,因此将ACK_I置低。

2018-07-26 09:01

Wishbone B.3总线。以类似的方式,Altera引入了自己的互连方案,称为Avalon Bus,SOPC Builder和Nios(II)系统就是围绕该方案制造的。Xilinx 还推出了自己的总线,称为片上外设总线与处理器本地总线 相结合。

2022-11-14 15:38

随着微电子设计技术与工艺的迅速发展,数字集成电路逐步发展到专用集成电路(ASIC),其中超大规模、高速、低功耗的新型FPGA的出现,降低了产品的成本,提高了系统的可靠性。同时,

2012-05-23 11:14