电子发烧友

1.1w次浏览

想请教各位前辈,wishbone在工作中很常用吗?我最近在学关于这个的代码,感觉很难懂,而时间又感觉不大够用,需要重点攻击, 所以想知道是否值得投入大量的时间去研究它。望各位前辈不吝赐教

2014-03-02 23:37

本文简要介绍了AMD 公司Am29LV160D 芯片的特点,并对WISHBONE总线作了简单的介绍,详细说明了FLASH memory 与WISHBONE 总线的硬件接口设计及部分Verilog HDL 程序源代码。

2011-06-23 16:32

WISHBONE总线,所以本设计的接口具有可移植性。 Am29LV160D芯片特点Am29LV160D是一种仅需采用3.0V电源进行读写的闪存。该器件提供了70ns、90ns、120ns读取时间,无需高速微处理器

2018-12-05 10:35

本文介绍的基于Wishbone总线的UART IP核的设计方法,通过验证表明了各项功能达到预期要求,为IP核接口的标准化设计提供了依据。此外,该IP核代码全部采用模块化的Verilog-HDL语言编写,

2011-06-10 11:47

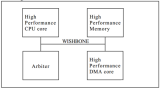

以 FPGA 技术为基础,以Verilog HDL 为载体,设计了遵守Wishbone 片上总线规范的IP 核接口,实现了片上系统的IP 核互联。

2010-01-13 15:09

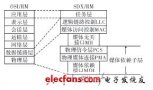

通用IO接口是Soc系统中非常重要的一种外围端口.本文完成了一种基于WISHBONE总线的GPIO_W B拉制器的逻拜设计和物理实现.文中较其体地介绍了GPIO_W B核的体系结构以及WISHBONE接Q和DMA传偷方式

2011-09-21 16:57

该设计采用了自顶向下的模块化划分和有限状态机相结合的方法,由于其应用了标准的Wishbone总线接口,从而使微机系统与串行设备之间的通信更加灵活方便。验证结果表明,这种新的架构

2011-10-19 15:01

注意3.30:在总线周期期间置位ERR_I信号,会立即结束该周期,意味着从机通知主机在该周期期间发生了错误。当从机逻辑电路检测到错误,便会置位ERR_I信号。例如,如果从机使用了奇偶校检,当发生错误时,从机便会通过ERR_I做出反应。

2018-07-12 08:38

介绍了基于硬件描述语言Verilog HDL设计的SDX总线与Wishbone总线接口转化的设计与实现,并通过Modelsim进行功能仿真,在QuartusⅡ软件平台上综合,最终在Altera公司的CycloneⅢ系列FPGA上调试。实验

2012-01-11 10:21

在以上介绍的三种总线中,CoreConnect虽免费不过需要IBM 公司许可,ARM 没有明确的正式说法,可能也会免费,而Wishbone 是绝对免费的。三种总线都是同步的总线,使用时钟上升沿驱图7 8-bit SLAVE输出端口动和采样信号。

2018-08-11 09:14