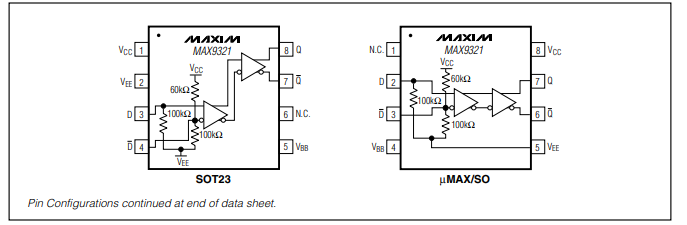

MAX9321/MAX9321A是一种低扭曲、差分接收器/驱动器,设计用于时钟和数据分配。差分输入经过调整后,可以允许单端输入,只需将片上V~BB~电源接到一个输入端作为参考电压即可。

2025-04-16 10:37

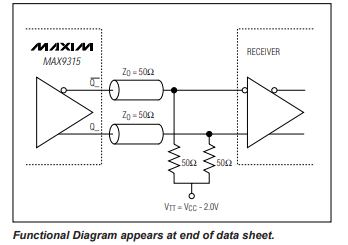

MAX9315是低扭曲、1:5差分驱动器,设计用于时钟和数据分配。这种器件允许选择两路输入之一。所选择的输入再生5路差分输出。差分输入经过调整后,可以允许单端输入,只需将片上V~BB~电源接到一个输入端作为参考电压即可。

2025-05-19 10:49

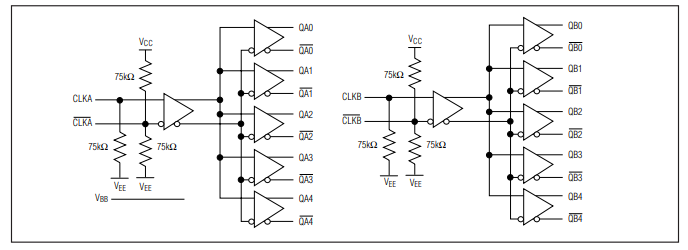

MAX9312/MAX9314是低扭曲、双路1:5差分驱动器,设计用于时钟和数据分配。这些器件接受两路输入。每个输入再生5路差分输出。差分输入经过调整后,可以允许单端输入,只需将片上V~BB~电源接到一个输入端作为参考电压即可。

2025-05-19 11:25

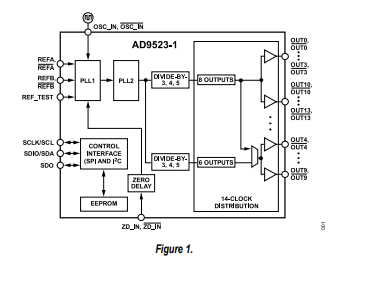

AD9523-1提供低功耗、多路输出时钟分配功能,具有低抖动性能,还配有片内PLL、VCO和两个VCO分频器。片内VCO的调谐频率范围为2.94 GHz至3.1 GHz。 AD9523-1旨在满足长期演进(LTE)和多载波GSM基站设计的时钟要求。它依靠外部VCXO清除参考抖动,以满足严格的低相位噪声要求,从而获得可接受的数据转换器信噪比(SNR)性能。

2025-04-10 15:35

MAX9320/MAX9320A是一种低扭曲、1:2差分驱动器设计用于时钟和数据分配,由一路输入再生2路差分输出。差分输入经过调整后,可以允许单端输入,只需外加基准电压即可。

2025-05-19 11:51

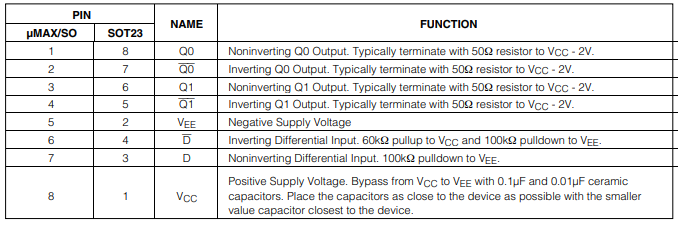

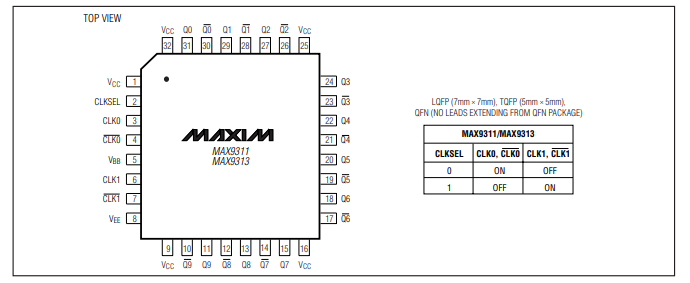

MAX9311/MAX9313是低扭曲,1:10差分驱动器,设计用于时钟和数据分配。这些器件允许选择两路输入之一。所选择的输入产生10路差分输出。差分输入经过调整后,可以允许单端输入,只需将片上V~BB~电源接到一个输入端作为参考电压即可。

2025-05-19 11:21

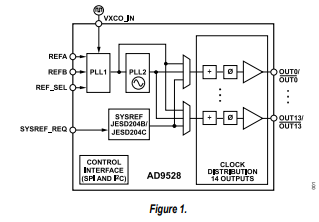

AD9528是一款双级PLL,集成JESD204B/JESD204C SYSREF发生器,可用于多器件同步。第一级锁相环(PLL) (PLL1)通过减少系统时钟的抖动,从而实现输入基准电压调理。第二级PLL (PLL2)提供高频时钟,可实现来自时钟输出驱动器的较低积分抖动以及较低宽带噪声。外部VCXO提供PLL2所需的低噪声基准电压,以满足苛刻的相位噪声和抖动要求,实现可以接受的性能。片内VCO的调谐频率范围为3.450 GHz至4.025 GHz。集成的SYSREF发生器输出单次、N次或连续信号,并与PLL1和PLL2输出同步,以便对齐多个器件的时间。

2025-04-10 10:19

、SSTL2-I、SSTL2-II、SSTL3-I、SSTL3-II、HSTL-I、HSTL-II、HSTL-III、HSTL-IV、HSUL_12、POD1

2021-01-02 09:45

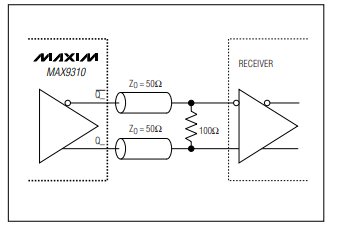

MAX9310是一种快速,低扭曲1:5差分驱动器,具有可选的LVPECL/HSTL输入端和LVDS输出端,设计应用于时钟分配。这种器件的特点是具有345ps的极低传输延迟和45.5mA的电源电流。

2025-05-19 10:00

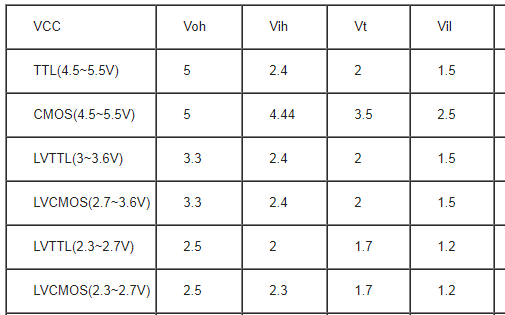

、GTL、PGTL、CML、HSTL、SSTL等。 TTL电平 TTL:Transistor-Transistor Logic 三极管结构。TTL电平常用的一般分为2种,分别是3.3V和5V,不论是

2022-10-27 10:39