描述SY89809AL是一款高性能总线时钟驱动器,具有9个差分高速收发器逻辑(HSTL)输出对。该器件设计用于低压(3.3V/1.8V)应用,需要大量输出来驱动精确对齐的超低偏斜信号至目的地。输入通

2023-12-14 11:18 深圳芯领航科技有限公司 企业号

特性单端LVCMOS输出LVCMOS频率高达200MHz附加抖动:25fs(10kHz-20MHz@156.25MHz )输出间偏斜:10ps器件间偏斜:30ps(最大值)输入输出延迟:低于2ns(典型值)单端LVCMOS/LVTTL/HSTL输入电源电压:2.5/3.3V±5%

2021-12-17 10:45 南京极景微半导体有限公司 企业号

、1.5V、 1.8V、2.5V、3.3V IO 标准 支持HSTL、SSTL存储接口标准 支持MIPI D-PHY接口标准 支持LVDS 、 MINI-L

2025-01-16 15:15 深圳市点面线科技有限公司 企业号

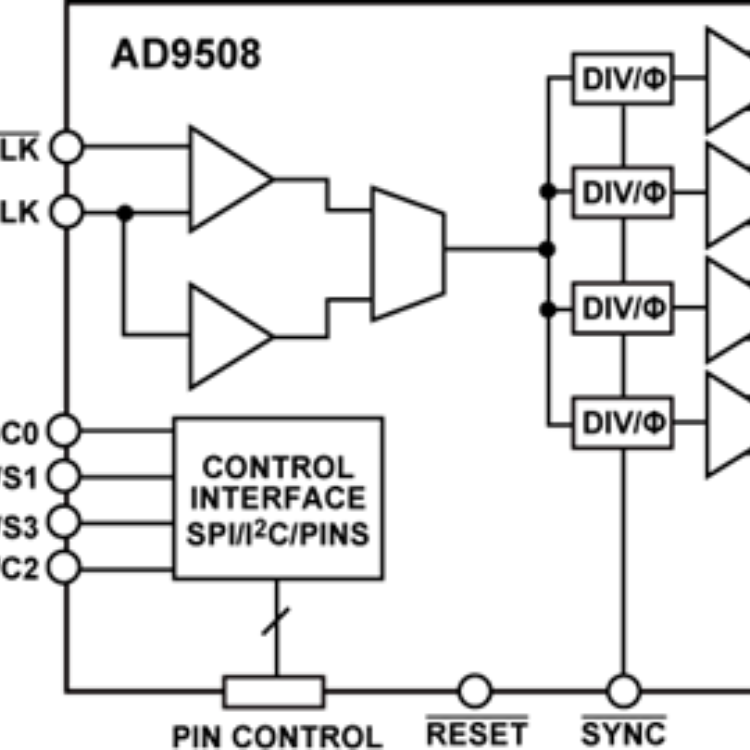

控制线路用于确定固定模块输出是LVDS输出还是CMOS输出。 时钟输入接受各种单端和差分逻辑电平,包括LVPECL、LVDS、HSTL、CML和CMOS。表

2023-02-13 15:27 深圳市聚成恒信电子科技有限公司 企业号

支持多种逻辑电平类型。包括LVDS (1.65 GHz)、HSTL (1.65 GHz)和1.8 V CMOS (250 MHz)。在1.8 V CMOS输出模式

2023-02-13 15:06 深圳市聚成恒信电子科技有限公司 企业号

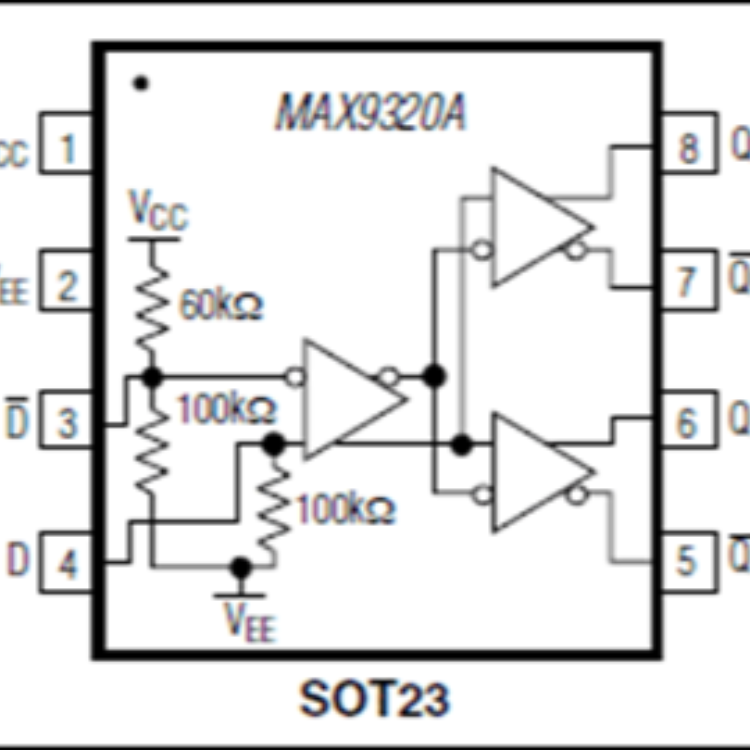

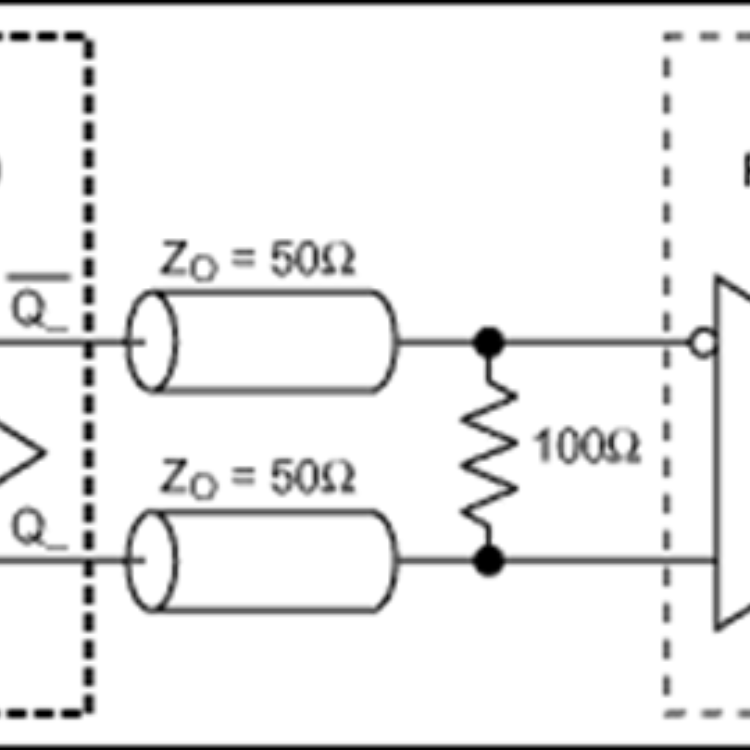

/MAX9320A具有超低传输延迟(208ps)、20ps的器件至器件扭曲和6ps的输出至输出扭曲以及最大30mA的电源电流等特性,使其尤其适合于时钟分配。为与差分HSTL

2023-07-12 15:22 深圳市聚成恒信电子科技有限公司 企业号

MAX9310是一种快速,低扭曲1:5差分驱动器,具有可选的LVPECL/HSTL输入端和LVDS输出端,设计应用于时钟分配。这种器件的特点是具有345ps的极低传输延迟和45.5mA的电源电流

2023-07-12 13:44 深圳市聚成恒信电子科技有限公司 企业号

、幅度不小于100mV的差分信号。输入完全兼容于LVDS、LVPECL、HSTL和CML差分信号标准,输出满足LVPECL电平,具有足够的电流驱动50Ω传输线。M

2023-07-12 11:12 深圳市聚成恒信电子科技有限公司 企业号