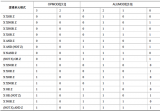

可以选择包含所声明变量的特定地址区域,可以访问宽为 1 位、8 位、16 位或 32 位的区域,这种访问类型称之为“片段访问”(Slice access)。

2022-03-14 14:16

【导读】博途中不但变量数据类型的隐式转换很好用,而且对于变量的Slice(直译:片或部分)寻址也很方便,下面就来说下S7-1200/1500如何以用Slice方式对变量进行寻址。

2023-04-07 10:58

对比两个struct或者map,slice是否相等是大家经常会有的需求,想必大家也都接触过很多对比的方式,比如==,reflect.DeepEqual(),cmp.Equal()等。

2024-01-08 18:20

创建一个 S7-1200 的项目,在程序块中新建一个 DB 块(优化的块访问),创建一个变量,数据类型为 DWord,可以看到该变量没有绝对地址,如下图所示。

2023-03-27 16:44

Spartan-6每个CLB模块里包含两个SLICE。CLB通过交换矩阵和外部通用逻辑阵列相连,如图2-1和图2-2所示。底部的SLICE标号为SLICE0,顶部的SLICE

2017-02-11 09:53

Spartan-6的每个SLICE 有8个存储元件,可以实现存储功能。

2017-02-11 09:56

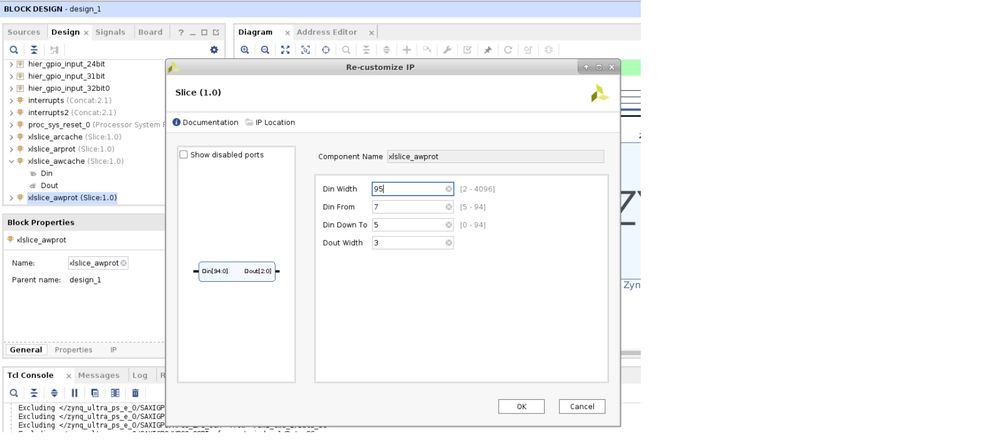

MPSoC 为PL提供了96个GPIO,通过EMIO管脚链接到PL。 普通PL设计,一般只会用到几个GPIO管脚。可以使用Vivado IPI中的Slice IP, 从其中分出指定数量的管脚

2020-11-04 14:57

为了适应越来越复杂的DSP运算,Virtex-6中嵌入了功能更强大的DSP48E1 SLICE,简化的DSP48E1模块如图5-16所示。

2017-02-11 09:17

为了适应越来越复杂的DSP运算,Spartan-6在Spartan 3A DSP模块DSP48A 基础上,不断进行功能扩展,推出了功能更强大的DSP48A1 SLICE。

2017-02-11 08:53

如果时钟同时驱动I/O和Slice中的逻辑资源,且负载小于2000时,可通过CLOCK_LOW_FANOUT属性对相应的时钟net进行设置,最终可使工具将该时钟驱动的所有负载放置在同一个时钟域内。通过命令report_clock_utilization生成的报告可查看每个时钟的负载,如下图所示。

2018-11-07 11:08