在同步模式下,最大 SCLK 频率为 8 MHz。在异步模式下,最大 SCLK 频率限制为 7.5 MHz。引脚 CLKM 上的信号不需要导出 SCLK,可以禁用以降低功耗和杂散发射。

2022-08-11 15:47

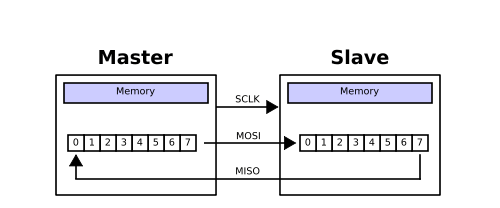

无论实现读还是写功能,都先要提供SCLK。假如FPGA系统工作时钟40MHz,我们可以利用计数器产生一个n分频的时钟作为SCLK,本例中n取8,SCLK频率5MHz。SCLK

2020-09-07 17:15

SPI标准包括四种模式,由SCLK的极性以及数据与SCLK之间的相位关系定义。时钟极性 (CPOL) 由 SCLK 的空闲状态决定。如果空闲状态为低,则 CPOL 为 0。如果空闲状态为高,则

2023-01-12 17:05

时钟极性(CPOL)和时钟相位(CPHA)用于设定从设备何时采样数据。CPOL决定SCLK为高时总线为空闲(CPOL=1)还是SCLK为低时总线为空闲(CPOL=0)。CPHA决定在SCLK的哪一个边沿将数据写入。

2020-07-17 15:59

SPI的CPOL,表示当SCLK空闲idle的时候,其电平的值是低电平0还是高电平1:CPOL=0,时钟空闲idle时候的电平是低电平,所以当SCLK有效的时候,就是高电平,就是所谓的active-high。

2023-04-10 16:21

74HC595内含8位串入,串/并出移位寄存器和8位三态输出锁存器。寄存器和锁存器分别有各自的时钟输入(SCLK和SLCK),都是上升沿有效。 当SCLK从低到高电平跳变时,串行输入数据(

2012-08-08 13:43

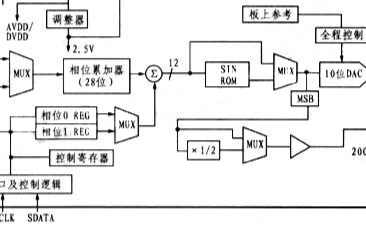

AD9833有3根串行接口线,与SPI、QSPI、MI-CROWIRE和DSP接口标准兼容,在串口时钟SCLK的作用下,数据是以16位的方式加载到设备上,时序图如图3所示,FSYNC引脚是使能引脚

2020-07-27 15:12

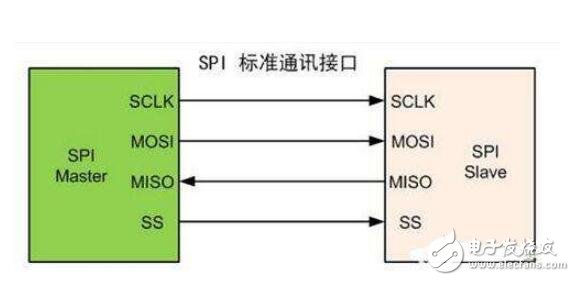

SPI, 串行外围设备接口。高速的,全双工的,同步通信总线。有四个引脚:SDI(数据输入),SDO(数据输出),SCLK(时钟),CS(片选)。

2018-03-08 09:39

。配置GPIO片选,推挽输出,上拉;SCLK、MOSI、MISO所用到的引脚为复用功能;SCLK下拉,MOSI推挽复用,MISO无推挽。下面我们来看看具体程序设计实现吧。

2018-01-15 16:51

cs5550 c程序:AD转换芯片cs5550的读写c语言读写程序 void write_CS5550(uchar data_to_send) // { uchar i; AD_SCLK=0; // AD_CS =0; Delay_us(20);

2008-07-19 12:00