SPI标准包括四种模式,由SCLK的极性以及数据与SCLK之间的相位关系定义。时钟极性 (CPOL) 由 SCLK 的空闲状态决定。如果空闲状态为低,则 CPOL 为 0。如果空闲状态为高,则

2023-01-12 17:05

。配置GPIO片选,推挽输出,上拉;SCLK、MOSI、MISO所用到的引脚为复用功能;SCLK下拉,MOSI推挽复用,MISO无推挽。下面我们来看看具体程序设计实现吧。

2018-01-15 16:51

I2S(Inter-IC Sound Bus)是飞利浦公司为数字音频设备之间的音频数据传输而制定的一种总线标准。I2S有3个主要信号:1.串行时钟SCLK,也叫位时钟,即对应数字音频的每一位

2019-03-05 10:14

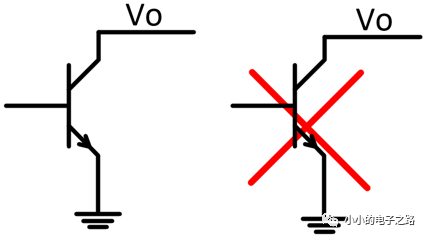

作为电路中最常见的电子元器件之一,电阻可以实现限流、隔离、上下拉等不同功能。以上拉为例,IIC通信接口SDA和SCLK都需要通过电阻实现上拉输入/输出。那么,电阻是如何实现上下拉功能的呢?

2023-11-13 18:23

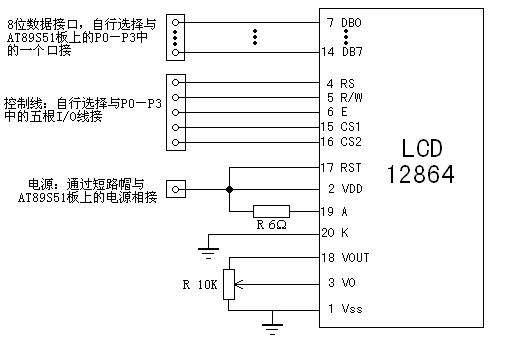

#i nclude #i nclude sbit SCLK =P1^3 //E sbit SID =P1^4; //RW sbit RST =P1^2; // low

2018-11-12 15:19

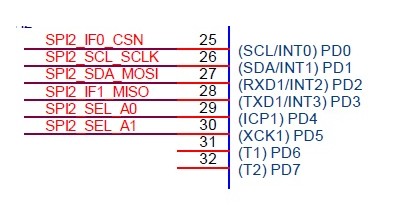

CSN(IF0)、SCLK(SCL)、RSTN、MOSI(SDA)、MISO(IF1)、AC0(GPIO0)、AC1(GPIO1)(这些管脚中的RSTN、AC0、AC1由FPGA控制),括号内是管脚

2018-12-06 15:28

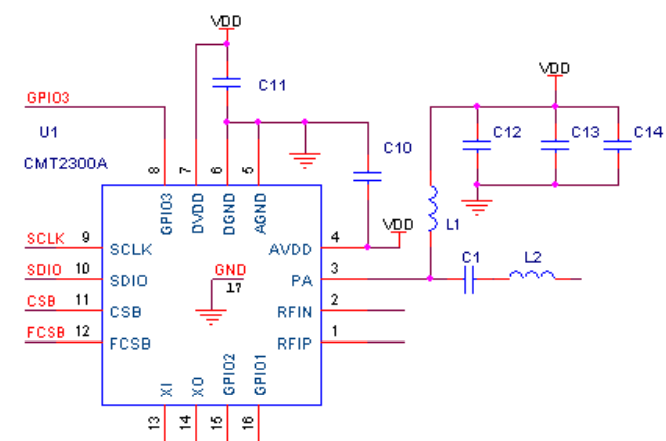

情况下,串口 CSB,FCSB,SDIO,SCLK 管脚容易受到干扰,功率输出(20dBm)越大,工作频率越低,受干扰的概率越大。

2019-09-21 11:50

传输率约100kbit/s。 程序中只用了MOSI,/SS,SCLK信号,没有用MISO信号。#include

2018-12-28 15:23

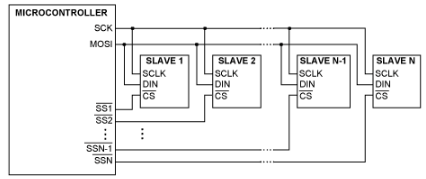

标准SPI™/QSPI/™ MICROWIRE™兼容微控制器通过3线或4线串行接口与其从器件通信。典型接口包括片选信号(/CS)、串行时钟(SCLK)、数据输入信号(DIN),偶尔还包括数据输出信号(DOUT)。与I2C系统中通常一样,可单独寻址的设备与总线上的单个设备轻松通信。

2023-02-27 14:14

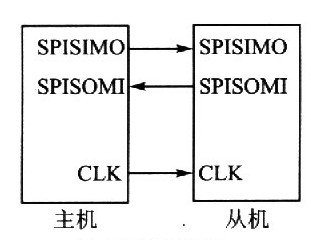

介绍SPI总线由开发,是一种,由四个IO口组成:CS、SCLK、MISO、MOSI;通常用于CPU和外设之间进行通信,常见的SPI总线设备有:TFTLCD、QSPIFLASH、时钟模块、IMU等

2025-02-26 19:00 RT-Thread官方账号 企业号