1.现象:GD MCU检测到设备,升级一次后,找不到设备,如下图所示;2.排查:检查代码,有GD MCU的两SWD、SCLK设置成IO口的代码(升级后,把SWD的两脚设置成IO,后边再也升级不了

2021-10-25 11:51

ADS7886是一个12位的1-MSPS模数转换器(ADC)。该装置包括具有固有采样和保持的基于电容的SAR A/D转换器。每个设备的串行接口由CS和SCLK信号控制,用于与微处理器和DSP的无缝连接。输入信号用CS的下降沿采样,SCLK用于转换和串行数据输出。

2018-05-25 16:40

、26 MHz),等等) 该设备可以工作在主时钟模式或从时钟模式。在从模式下,LRCK和外部提供SCLK,而LRCK和SCLK必须从具有特定速率的系统时钟。在主模式下,lrk和sclk内部派生自设备主时钟。

2023-11-28 14:49

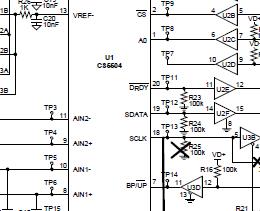

CS5504与CAPTURE板接口电路的修改(为了产生SCLK信号):

2009-06-10 10:37

CS5509与CAPTURE板接口电路的修改(为了产生SCLK信号):

2009-06-10 10:39

ADS7883是一个12位的3-MSPS模数转换器(ADC)。该装置包括具有固有采样和保持的基于电容的SAR A/D转换器。该设备中的串行接口由CS和SCLK信号控制,用于与微处理器和DSP的无缝连接。输入信号用CS的下降沿采样,SCLK用于转换和串行数据输出。

2018-05-25 17:12

SID PA6 #define SCLK PA7 #define Set_CS() DDRA |= (1《《CS);PORTA |= (1《《CS) #define Set_SID() DDRA

2017-11-27 14:15

, which is the writing of an instruction byte into the AD9777 coincident with the first eight SCLK rising edges. The instruction byte provides t

2009-09-18 08:43

模式?何时收发数据?第一,作为主机,SPI在建立起通信什么时刻发送数据呢?什么时刻进行数据采样?抛出俩个新的名词:时钟极性(CPOL)和时钟相位(CPOA)。CPOL:决定SCLK时钟信号在空闲时的状态 0:空闲状态时,SCLK保持低电平 1:空闲

2021-12-22 19:16

discrete channels, consequently the resultant SCLK and FS signals transmitted by the master codec

2017-05-27 15:18