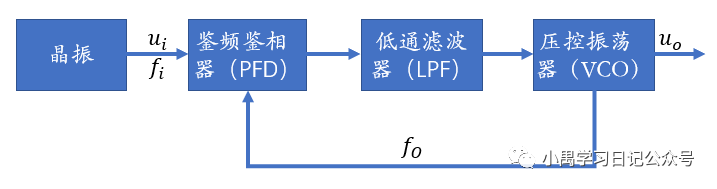

图显示鉴频鉴相器(PFD)的常见实现方案,该类器件基本上都由两个D型触发器组成。

2012-06-08 16:04

芯片要工作就需要读取指令,解析指令然后运行指令,需要在某种固定的周期性运动的设备驱动下有条不紊的进行,它就是`频率`。

2023-03-02 16:23

要记住的一个关键点是,这两个指标都只涉及危险的故障,这些故障会阻止系统维护安全或实现安全状态。诊断检测到的危险故障实际上是安全的,并且从指标中排除。

2023-06-29 11:33

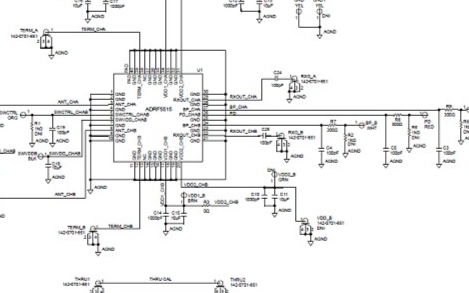

ADRF5515 是一款双通道、集成式射频前端、多芯片模块,专为时分双工 (TDD) 应用而设计。该器件的工作频率范围为 3.3 GHz 至 4.0 GHz。ADRF5515 配置为双通道,具有级联、两级、LNA 和高功率硅 SPDT 开关。

2021-06-12 09:34

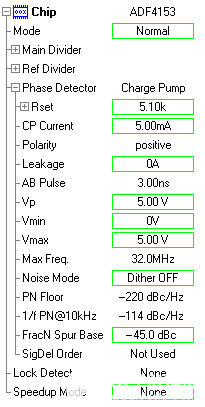

频率合成器在锁相环 (PLL) 中工作,其中相位/频率检测器 (PFD) 将反馈频率与参考频率的分频版本进行比较(图 1)。PFD的输出电流脉冲经过滤波和积分以产生电压。该电压驱动外部压控振荡器 (VCO) 增加或降低输出频率,从而将

2023-02-03 10:50

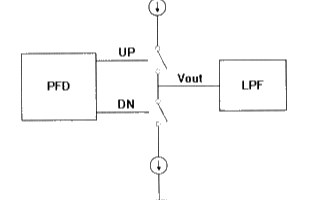

图l是典型的电荷泵结构。此处电荷泵为两个受鉴频鉴相器(PFD)输出信号控制的开关电流源,它与后面的环路滤波器共同作用,将PFD的逻辑信号转化为电压信号,该电压信号进而调节压控振荡器的振荡频率。

2021-03-11 09:30

在这篇文章中,我们将介绍鉴频鉴相器(PFD)的工作原理。

2023-11-22 14:49

校准完成后,PLL的反馈操作使VCO锁定于正确的频率。锁定速度取决于非线性周跳行为。PLL总锁定时间包括两个部分:VCO频段校准时间和PLL周跳时间。VCO频段校准时间仅取决于PFD频率;PFD频率越高,锁定时间越短。

2018-05-11 15:14

许多工程师对如何选择参考频率感到困惑,但参考频率和输出频率阶跃之间的关系很简单。对于整数N分频PLL,输出频率阶跃等于鉴频鉴相器(PFD)输入端的频率,即参考频率除以参考分频器R。对于小数N分频

2023-01-30 15:25

ADF4002由低噪声数字鉴频鉴相器(PFD)、精密电荷泵、可编程参考分频器和可编程N分频器组成。14位参考计数器(R计数器)允许PFD输入端的REFIN频率为可选值。如果频率合成器与一个外部环路滤波器和电压控制振荡器(VCO)一起使用,则可以实现完整的锁相环(P

2013-10-22 15:15