对于mig与DDR3/DDR2 SDRAM的读写时序我们不需要了解太多,交给mig就可以了。

2019-03-03 11:11

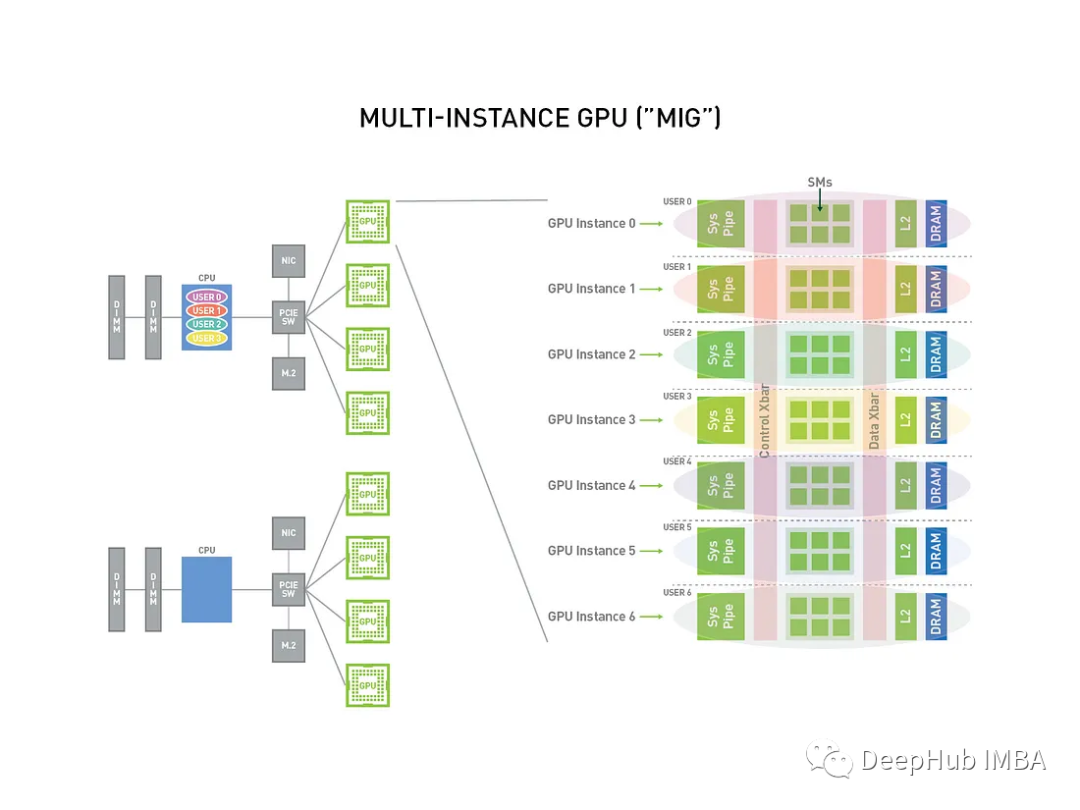

使用多实例GPU (MIG/Multi-Instance GPU)可以将强大的显卡分成更小的部分,每个部分都有自己的工作,这样单张显卡可以同时运行不同的任务。本文将对其进行简单介绍并且提供安装和使用的示例。

2023-10-11 14:42

TIG焊一般是一手持焊枪,另一只手持焊丝,适合小规模操作和修补的手工焊。

2019-11-05 10:47

我们通过Configuration,Package,Speed...等DDR3的命名可知道DDR3的容量,封装,速度等级等信息。

2019-03-03 11:04

软开关型脉冲MIG焊接电源系统整体结构如图1所示,由主电路、控制电路、驱动电路3个主要部分组成。系统采用目前较为常用的AC/ DC/AC/DC的逆变模式,脉冲开关信号来自单片机给出的控制指令,经驱动和放大后,为功率开关管提供固定频率为20 kHz的高频脉冲开关信号。

2018-04-13 08:25

下面是调用的DDR3模块的,模块的倒数第二行是,模块的时钟输入,时钟源来自PLL产生的系统时钟的倍频。

2025-05-03 10:21

基于vivado2020.1和zcu102开发板(rev1.1)开发项目,工程涉及DDR4(MIG)和PL端多个读写接口交互的问题,通过AXI interconnect进行互联和仲裁(采用默认配置)。

2023-12-01 09:04

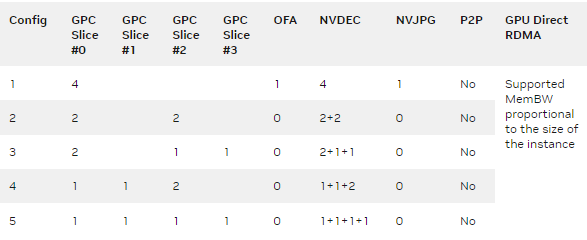

多实例 GPU ( MIG )是 NVIDIA H100 , A100 和 A30 张量核 GPU ,因为它可以将 GPU 划分为多个实例。每个实例都有自己的计算核心、高带宽内存、二级缓存、 DRAM 带宽和解码器等媒体引擎。

2022-10-11 10:07

基于vivado2020.1和zcu102开发板(rev1.1)开发项目,工程涉及DDR4(MIG)和PL端多个读写接口交互的问题,通过AXI interconnect进行互联和仲裁(采用默认配置)。一个完整控制周期内(约100ms),各端口读写情况如下(AWSIZE均为4)。

2022-06-15 11:59

这篇文章我们讲一下Virtex7上DDR3的测试例程,Vivado也提供了一个DDR的example,但却是纯Verilog代码,比较复杂,这里我们把DDR3的MIG的IP Core挂在Microblaze下,用很简单的程序就可以进行DDR3的测试。

2022-08-16 10:28