Random Access Memory的缩写,即同步动态随机存取存储器。本文首先介绍了DDR工作原理及结构图,其次阐述了DDR DQS信号的处理,具体的跟随小编一起来了解一下。

2018-05-23 16:07

在i.MX RT060项目(采用QSPI Flash)的实际应用中,有客户反馈,其在设计阶段并未预留DQS信号引脚,而是将该引脚作为GPIO用于控制关键外设的开关,这导致程序无法正常运行。在此背景下

2025-06-16 11:30

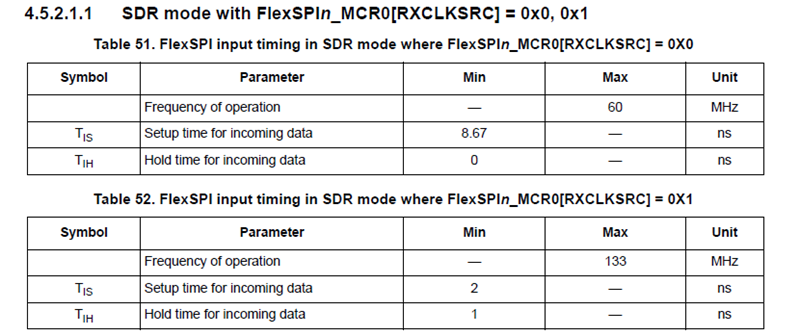

我们翻开 i.MXRT1170 的数据手册(Data Sheet)找到 FlexSPI parameters 小节里的如下内容,就很清楚了。

2023-06-02 17:53

本设计咨询涵盖如下 Versal DDRMC 设计:使用对应 LPDDR4 和 x8 或 x16 DDR4 组件接口的 DQS 字节组管脚交换所生成的设计。

2022-08-09 11:33

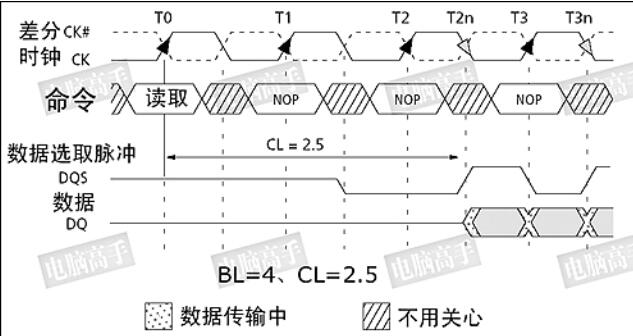

通过单次触发得到一个读或者写的波形,读的波形是DQS和DQ的相位是基本相同的。写的波形是DQS和DQ的相位基本上是90度。

2023-10-17 16:00

CK/CK# 全局差分时钟,所有控制和地址输入信号在CK上升沿和CK#的下降沿交叉处被采样,输出数据选通(DQS、DQS#)参考与CK和CK#的交叉点。

2022-08-09 15:04

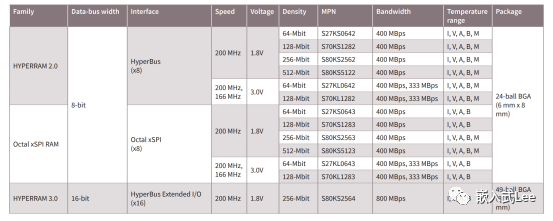

PSRAM的时序比较简单,主要根据各个时序图理解每个时序阶段,及其参数。重点要理解DQS/DM是谁驱动的,代表什么意思, 数据采样的时间即DQS上升沿延迟数据建立时间之后采样。

2023-06-08 11:30

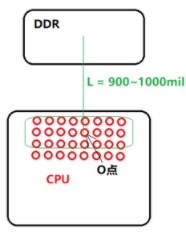

数据信号与DQS做等长。为啥要做等长?大家会说是要让同组信号同时到达接收端,好让接收芯片能够同时处理这些信号。

2020-01-06 15:23

对于Layout人员来说,对于DDR这一块,可能主要关注的是信号线之间的等长。下面我们也来复习一下,DDR各组信号需要满足的时序关系:地址/命令,控制和时钟之间等长;DQ与之对应的DQS组内等长;DQS与CLK之间有一个相对宽松的等长关系。

2018-09-15 10:58

近日,摩尔线程获得由德世爱普认证(上海)有限公司(简称:DQS)颁发的ISO9001:2015质量管理体系认证证书,这标志着摩尔线程在GPU芯片及相关产品的设计和研发、销售与生产外包管理等方面的质量管理能力达到国际标准。

2023-01-07 10:39