Random Access Memory的缩写,即同步动态随机存取存储器。本文首先介绍了DDR工作原理及结构图,其次阐述了DDR DQS信号的处理,具体的跟随小编一起来了解一下。

2018-05-23 16:07

在i.MX RT060项目(采用QSPI Flash)的实际应用中,有客户反馈,其在设计阶段并未预留DQS信号引脚,而是将该引脚作为GPIO用于控制关键外设的开关,这导致程序无法正常运行。在此背景下

2025-06-16 11:30

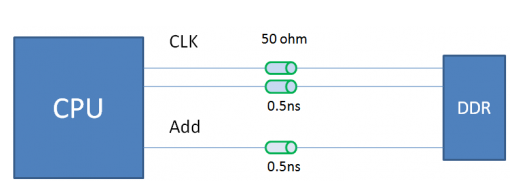

数据信号与DQS做等长。为啥要做等长?大家会说是要让同组信号同时到达接收端,好让接收芯片能够同时处理这些信号。

2020-01-06 15:23

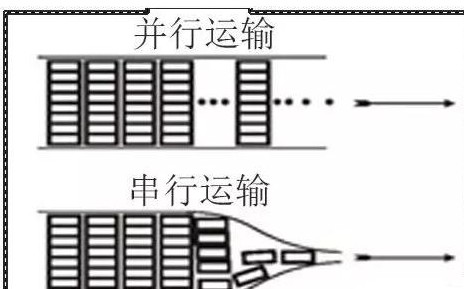

并行传输最好的例子就是存储芯片DDR,它是有一组数据线D0—D7,加DQS,DQM,这一组线是一起传输的,无论哪位产生错误,数据都不会正确的传送过去,只有重新传输。所以数据线每根线要等长,必须得绕几下才行。

2019-01-09 14:27

/命令信号与时钟做等长。数据信号与DQS做等长。为啥要做等长?大家会说是要让同组信号同时到达接收端,好让接收芯片能够同时处理这些信号。

2017-09-01 14:03

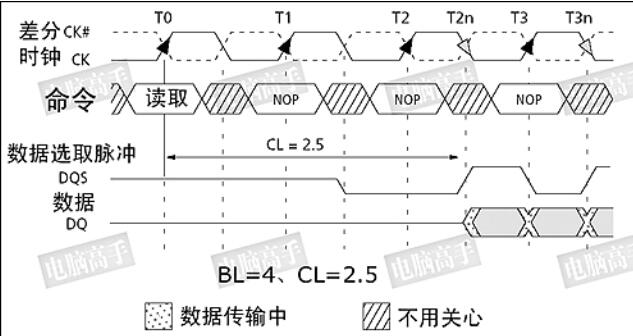

内存广泛应用于各类电子产品中,内存测试也是产品测试中的热点和难点。内存测试中最为关键的测试项目为DQ/DQS/CLK之间的时序关系。##Jitter Sim是力科示波器中的一个通过软件仿真的方法实现信号源的功能,该功能可以实现时钟信号,正弦信号,NRZ,RZ等种类多样的码型。

2014-01-06 14:31