一、装置简介QY-DQS08高级电气安装与维修实训考核装置按实际房间比例设计,利用房间内部的立体空间以培养学生电气安装技能为主,融电钳工技能实训、电气故障诊断和电气故障维修为一体的技能性实训装置

2021-09-08 06:03

一、装置简介1、QY-DQS10建筑电气设备实验装置采用正反二面开门的离墙式威图电气控制柜,且正反面同时都可以操作,柜体中宽度能保证两个学生同时合作接线实训的需要。柜门安装有四块大的玻璃,学生能通过

2021-07-09 07:14

architecture, two data words are fetchedfrom the memory array during a single read command. DDR SDRAMuses a strobe signal (DQS)

2009-03-28 14:43

Pin Name / Function Optional Function(s) Configuration FunctionT100 DQS for x8 in the T100B1 VREF0B1 IO INIT_DON

2009-05-14 10:53

SDRAM在读取期间和由内存控制器执行写入期间。DQS是edge--与的数据对齐读取和居中—与写入数据对齐。DDR SDRAM通过差分时钟工作(CK和CK;CK和CK的交叉走低将被称为CK)。命令

2022-06-27 14:56

/命令信号与时钟做等长。数据信号与DQS做等长。为啥要做等长?大家会说是要让同组信号同时到达接收端,好让接收芯片能够同时处理这些信号。那么,时钟信号和地址同时到达接收端,波形的对应关系是什么样的呢?我们通过仿真来看一下具体波

2017-11-28 11:34

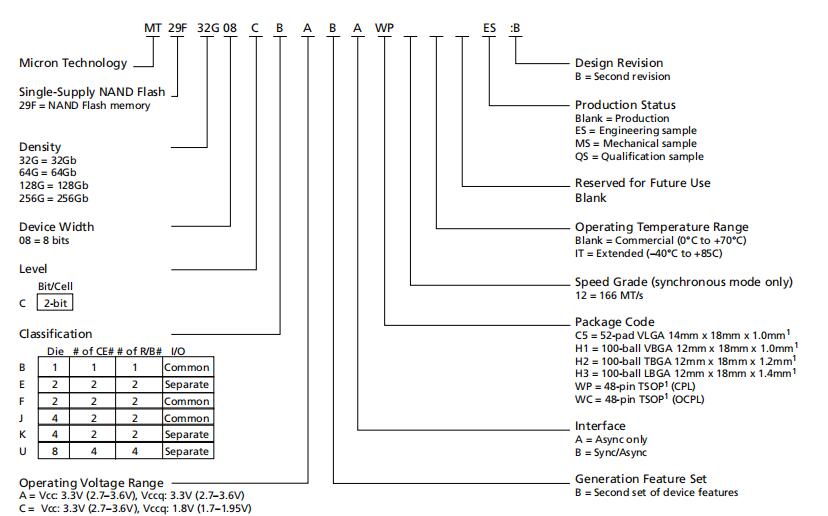

和RE#。附加信号控制硬件写保护(WP#)和监视设备状态(R/ b#)。该微米NAND闪存设备还包括用于高性能I/O操作的同步数据接口。当同步接口激活时,#变成CLK,而RE#变成W/R#。数据传输包括双向数据频闪(DQS)。

2021-03-29 09:46

进行管脚连接。 图1 接口总框图 EP3C16只有TOP和BOTTOM边的BANK支持200MHz DDR2接口(因为DDR2管脚的特殊要求,DQS、DQ、DM管脚在FPGA上都需要专用管脚

2011-05-03 11:31

据传输速率/引脚(DDR4-2666)。芯片的设计符合以下关键DDR4 SDRAM功能,如张贴的CAS、可编程CWL、内部(自)校准、,使用ODT引脚和异步复位的管芯端接。所有控制和地址输入都与一对外部提供的差分时钟同步。输入被锁存在差分时钟的交叉点(CK上升和CK下降)。所有I/O都与一对双向选通(DQS

2022-12-05 11:54

,共八组MEM_DAT[7..0],MEM_DM0,MEM_DQS0,MEM_DQS#0;MEM_DAT[15..8],MEM_DM1,MEM_DQS1,MEM_DQS

2015-02-03 14:13