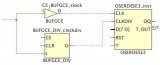

Clk引脚在芯片中是时钟信号的输入引脚。时钟信号在数字电路中起着非常重要的作用,它用于同步芯片内各个模块的操作,确保它们按照正确的时间序列执行任务。 时钟信号的输入通常由外部晶振或振荡器提供,被接入

2024-03-08 16:41

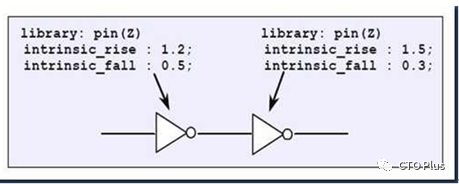

本文就帮助解决歪斜违规问题提供几个解决方案

2023-07-07 14:14

摘要:这是一篇关于时钟(CLK)信号质量的应用笔记,介绍如何测量抖动和相位噪声,包括周期抖动、逐周期抖动和累加抖动。本文还描述了周期抖动和相位噪声谱之间的关系,并介绍

2009-04-22 10:16

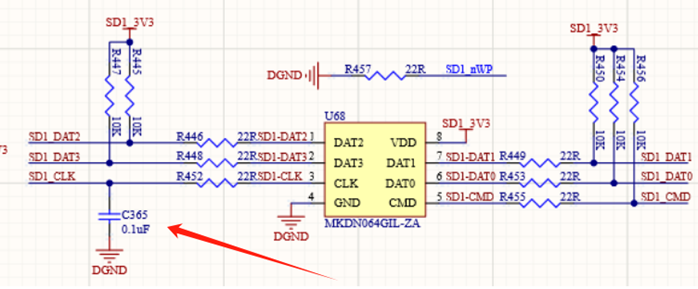

CLK的作用和注意事项 SD NAND的时钟引脚(CLK)的作用是提供一个时钟信号,用于同步数据传输。时钟信号是由主设备(如微控制器或存储控制器)提供的,用于确保SD NAND和主设备之间的数据交换

2024-01-29 16:44

电路板上的CLK是时钟信号线,用于同步各个电子器件的工作节奏。时钟信号告诉电子设备何时进行特定的操作,保证设备内部各功能模块的协调工作。本文将详细介绍电路板上CLK的用途、材料以及其工作原理。 一

2024-03-08 16:47

Verilog是一种硬件描述语言,用于描述数字电路的行为和特性。在Verilog中,时钟信号(clk)和线路是非常重要的,它用于同步电路中的各个模块,确保它们在同一时刻执行。

2023-10-10 15:41

村村通简介& 需求分析 改变现有的有线+调频广播模式,建立一套基于联通或者移动网络的村村通广播系统。 以行政村为单位安装网络广播系统,综合广播信息将覆盖全镇所有行政村,使得广大村民足不出户,就可闻知天下事。 村村通广播系统必须具备灾害预警功能。村村通广播为灾害预警大喇叭建设工作的重要工作平台,必须为气象/水利/农业局/林业局等部门提供接口。 播出的内容主要主要包括转播人民广播电台的节目,传达上级的会议精神,宣传计

2023-05-09 11:25

在数字电路中,"clk"通常指的是时钟信号(clock signal),它是一种周期性的信号,用于同步数字电路中的各种操作。时钟信号的高低电平有效性取决于具体的电路设计和应用场景。 1. 时钟信号

2024-07-23 11:24

CLK233型金属化聚酯薄膜电容器 CLK233 型金属化聚酯薄膜电容器采用阻燃塑料外壳,用阻燃环氧树脂封装,具有自愈性好、体积小、可靠性高等特点,适用于直流或脉动电路

2009-08-21 17:12

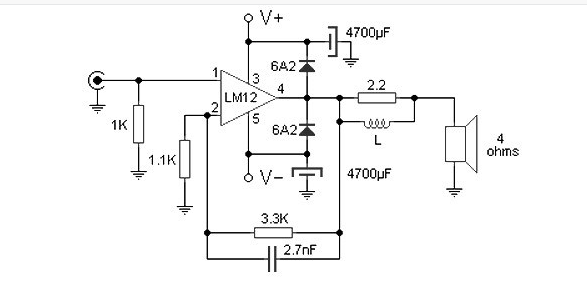

基于100W音频放大器的LM12CLK是可以简单组装的放大器电路之一。虽然结构简单,但产生的功率在2欧姆扬声器上可以达到150瓦,在4欧姆扬声器负载下可以达到100瓦。

2023-05-16 17:44