时序场景如下图所示,clk0和clk1两个时钟输入,经过BUFGMUX后,输出到后面的逻辑,但同时clk0和clk1还分别驱动了其他逻辑。

2023-12-19 12:56

时序场景如下图所示,clk0和clk1两个时钟输入,经过BUFGMUX后,输出到后面的逻辑,但同时clk0和clk1还分别驱动了其他逻辑。

2023-12-11 13:55

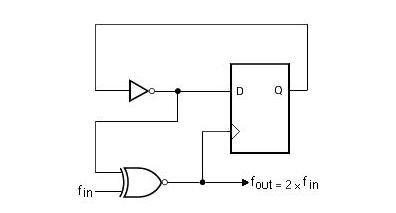

///////////////////////////////////////////////////////////////////////////// 4 module clk_mul( 5 input wire clk 6 , input wire rst

2020-11-09 14:53

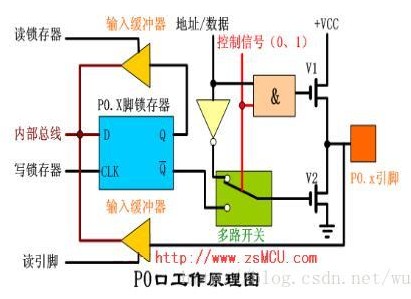

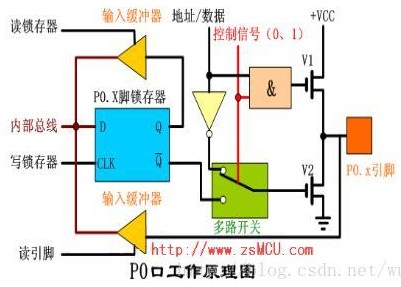

当D端和CP/CLK端同时有信号输入后突然撤掉CP/CLK信号时,D的值将会被保存到(“锁”)在器件内,此时Q和~Q端并没有信号输出,等下一个时序再次输入到CP/CLK端,Q和~Q将会正常输出D端传送的信号;

2019-01-21 15:52

当D端和CP/CLK端同时有信号输入后突然撤掉CP/CLK信号时,D的值将会被保存到(“锁”)在器件内,此时Q和~Q端并没有信号输出,等下一个时序再次输入到CP/CLK端,Q和~Q将会正常输出D端传送的信号;

2019-01-11 15:39

首先肯定是在本时钟域内的clk_en会先变低(invalid),之后才会使得另外时钟域内的clk_en变高(valid),这时另外一个时钟域内的时钟才能和clk_en相与输出。

2020-11-10 15:06

主要设计代码如下,通过localparam DIV_PEREM指定分频计数值。分频计数器为cnt,当enable为高时,cnt开始循环的从0递增到DIV_PEREM。Buad_clk在每次cnt==DIV_PEREM的时候就翻转一次,从而得到clk时钟的

2019-02-04 15:40

cordic算法verilog实现(简单版)(转载)module cordic(clk, phi, cos, sin); parameter W = 13, W_Z = 14; input clk; input [W_Z-1:0] phi; output[W

2017-02-11 03:06

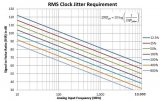

ADC的采样时钟输入端(CLK+和CLK−)。 通常,应使用变压器或电容将该信号交流耦合到CLK+引脚和CLK−引脚内。这两个引脚有内部偏置,无需其它偏置。 高速、高分

2017-12-19 04:10

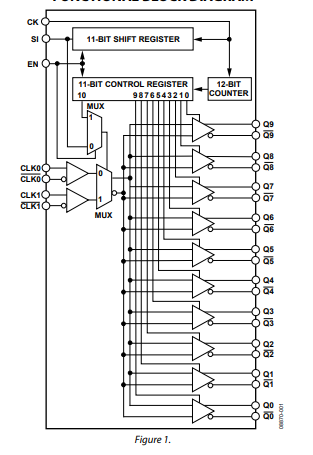

ADN4670是一款低压差分信号(LVDS)时钟驱动器,可以将一路差分时钟输入信号扩展为十路差分时钟输出。这款器件可以通过简单的串行接口进行编程,以便选择两路时钟输入之一(CLK0/CLK0 或

2025-04-10 16:19