通常情况下,HoldTiming是由工具自动去检查并满足的,人为可以干预的地方很少。如果你的设计在布局布线后,出现了hold timing违例的情况,那么你可以参考下本文提出的3点建议,看看能否改善

2017-02-08 05:22

今天我们要介绍的时序分析概念是 **时序路径** (Timing Path)。STA软件是基于timing path来分析timing的。

2023-07-05 14:54

Timing Con

2009-04-24 09:12

今天我们要介绍的时序基本概念是Timing arc,中文名时序弧。这是timing计算最基本的组成元素,在昨天的lib库介绍中,大部分时序信息都以Timing arc呈现。

2023-07-06 15:00

Implement Master-Slave Timing-Card Redundancy Using Maxim Timing ICs Abstract

2009-04-07 23:43

时序分析基本概念介绍——Timing Arc

2018-01-02 09:29

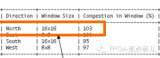

随着FPGA规模越来越大,设计本身的复杂度也同样增加。Xilinx UFDM中也经常提到了Design Complexity这样一个概念。Timing/Complexity/congestion

2017-02-08 05:46

今天想来聊一聊timing model。Top层在做STA的时候,为了速度的考量,有的时候不会把所有block都做flatten(展平化)处理

2023-12-06 14:03

默认report_timing中会出现换行的情况,如下图所示,如何避免换行呢?

2023-04-15 10:20

关键词:ISE , 时序约束 时钟上升沿和下降沿之间的时序约束 周期约束可以自动计算两个沿的的约束——包括调整非50%占空比的时钟。 例:一个CLK时钟周期约束为10ns,能够应用5ns的约束到两个寄存器之间。 不需要特定路径应用到这个例子中。 相关时钟域的约束 为一个时钟进行周期约束——以这个周期约束确定相关的时钟。 执行工具将根据它们的关系来决定如何处理跨时钟域。 DCM有多个输出: ——确定DCM输入时钟的周期约束 ——执行工具将会从这个

2018-09-26 07:44