时序分析基本概念介绍——Timing Arc

2018-01-02 09:29

然后会出现如下窗口, 使用GTD前, 需要有一个machine readable格式的timing report文件, 该文件可以通过report_timing -machine_readable

2020-05-19 16:14

《XDC 约束技巧》系列中讨论了XDC 约束的设置方法、约束思路和一些容易混淆的地方。我们提到过约束是为了设计服务,写入 Vivado中 的 XDC 实际上就是用户设定的目标,Vivado对 FPGA 设计的实现过程必须以满足 XDC 中的约束为目标进行。那我们如何验证实现后的设计有没有满足时序要求?又如何在开始布局布线前判断某些约束有没有成功设置?或是验证约束的优先级?这些都要用到 Vivado 中的静态时序分析工具。

2023-05-04 11:20

随着设计复杂度和调用 IP 丰富度的增加,在调试时序约束的过程中,用户常常会对除了顶层约束外所涉及的繁杂的时序约束感到困惑而无从下手。举个例子,用户在 XDC 里面并没有指定 set_false_path,为什么有些路径在分析时忽略了?那怎么去定位这些约束是哪里设定的?

2022-09-15 10:24

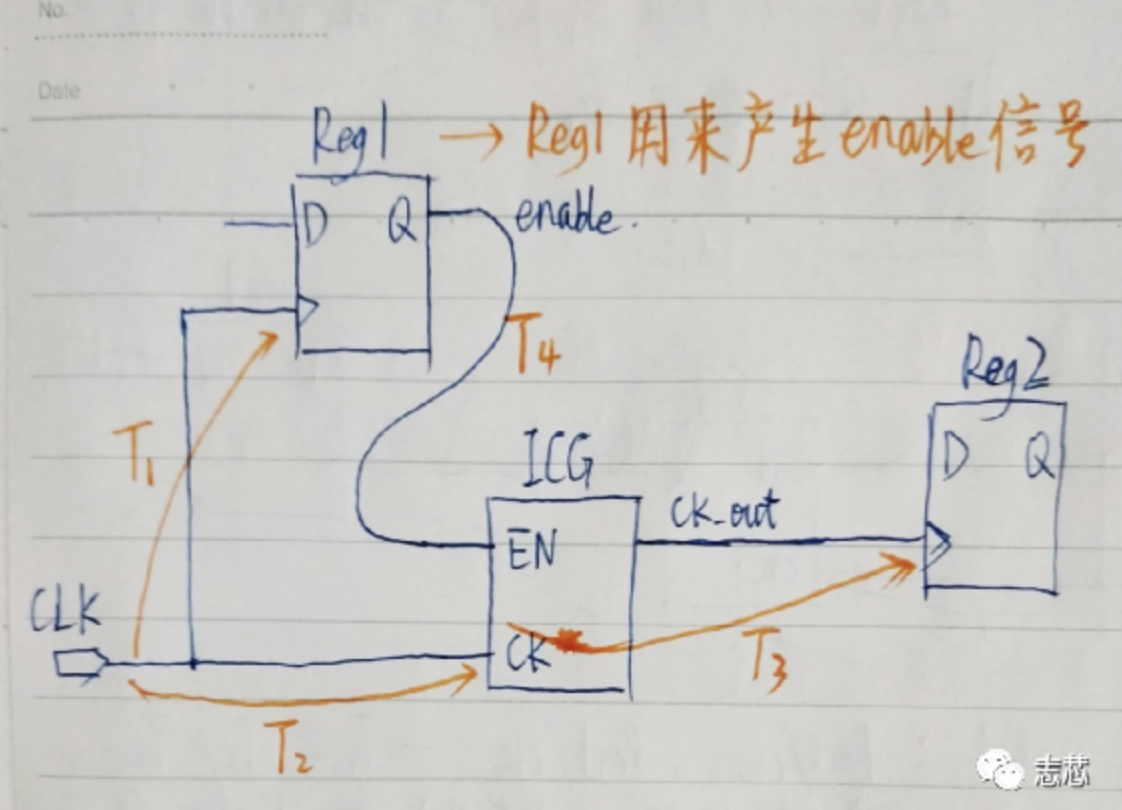

在不人工干预的情况下,tool默认会尝试把reg1的CK pin和Reg2的CK pin做平。

2023-11-23 17:21

Metal Fill或者说Dummy Metal对Timing是有影响的,在比较老的工艺、规模比较小的Design中影响是比较小的,甚至不考虑它们对于Timing的影响去流片也不是说一定不行(当然

2022-12-08 10:00

为一个IC工程师,最后拷问灵魂的时刻。明明是个小timing但就是死活修不好...

2017-10-11 09:31

Bit_timing 波特率定义,必须部分,但通常为空nodes 定义网络节点messages 定义消息和信号

2024-04-30 12:50

上述四个数值,无论是在timing report(通过report_timing_summary生成)还是design analysis report(通过report_design_analysis生成)中都有所体现。以timingreport为例,如下图所示,

2018-10-19 10:32

以上图中的Type选取Timing为例,Reports一栏可以浏览到的报告如下图所示。这里,这些报告之所以可见,是因为事先在设置Implementation Settings时,将其中的Report Options对应的Strategy设置为Timing Clos

2019-01-08 12:01