LVPECL到LVPECL的连接,分为直流耦合和交流耦合两种形式。

2023-08-28 15:32

前一篇文案介绍了LVDS,本篇介绍LVPECL(Low Voltage Positive Emitter Coupled Logi) 低压正射极耦合逻辑, 源自发射极耦合逻辑(ECL),采用正电源。

2023-04-20 11:37

在高速光通信系统中,LVPECL(低压正射极耦合逻辑)、PECL(正射极耦合逻辑)与 LVDS(低压差分信号)是常用的高速接口电平标准。LVPECL/PECL 以高速度、低噪声特性广泛应用于光模块

2025-08-08 10:48

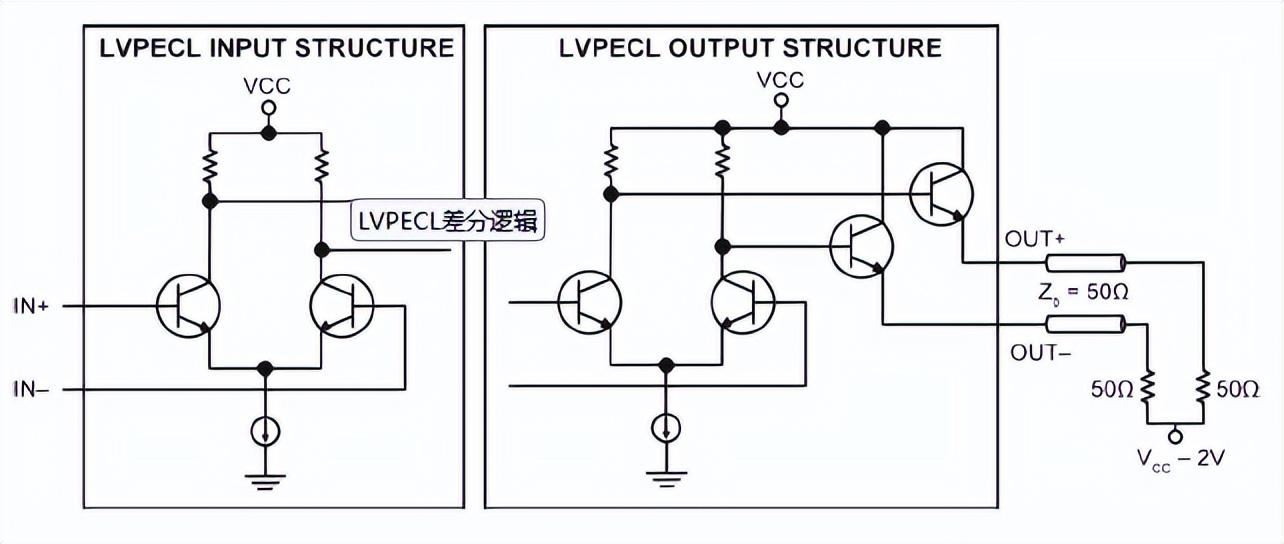

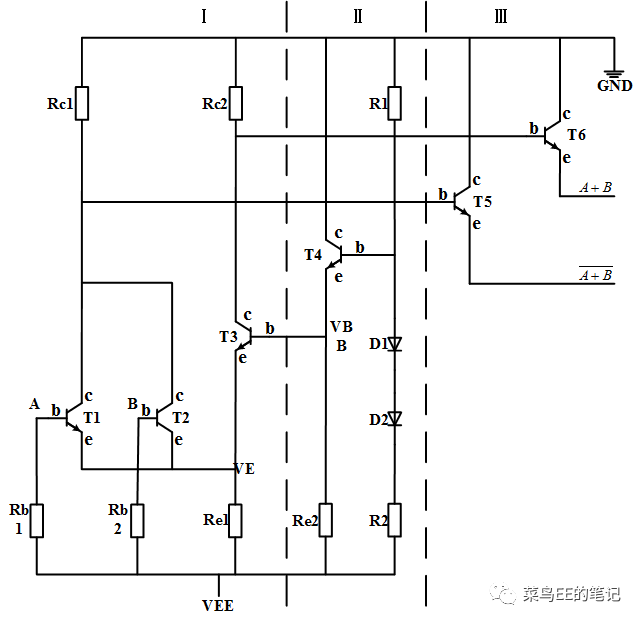

LVPECL电平是常用的一种逻辑电平,大部分资料对该电平的描述为:由ECL电平发展而来,但是对其逻辑电平门限的确定、为什么要加一个偏置电平以及LVPECL电平与ECL电平在电路结构上的差异鲜有论述。因此,对在学习该电平中遇到的困惑整理如下。

2023-09-21 17:04

LVPECL(低压正射极耦合逻辑)是一种输入输出(I/O)技术,从半导体工艺无法集成高性能P 型设备与高性能N 型设备起就已出现。因此,在随后的HCSL 和LVDS等高速接口中,需要外部无源器件来完成由P 型设备完成的任务。

2018-05-28 10:44

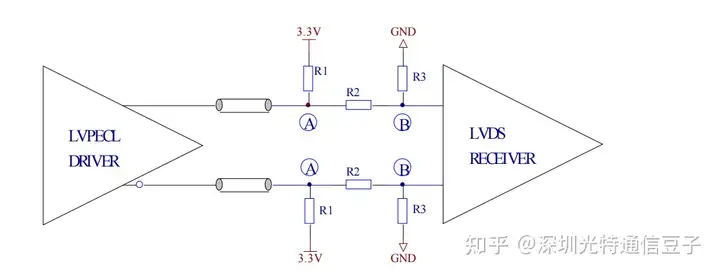

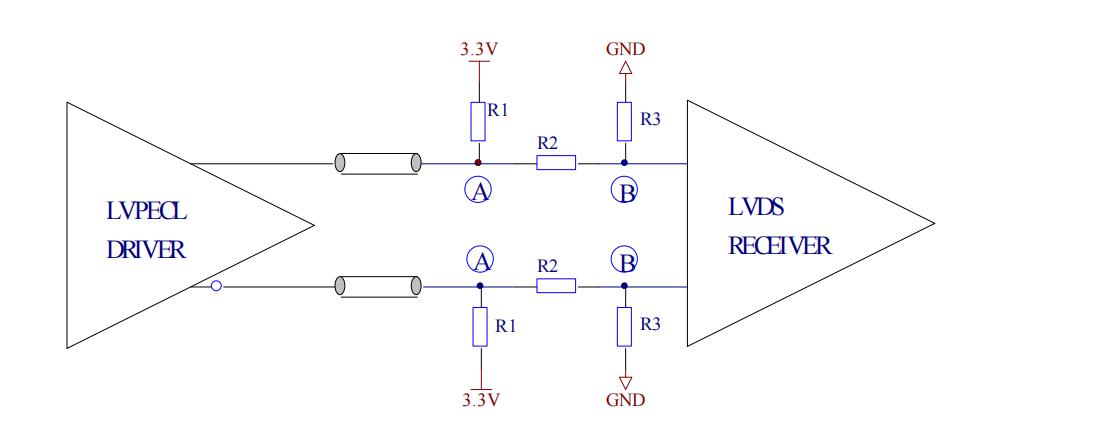

1. LVPECL 与LVDS 的互连 1.1 LVPECL 与LVDS 的直流耦合 LVPECL 到LVDS 的直流耦合结构需要一个电阻网络,如图5 中所示,设计该网络时有这样几点必须考虑

2025-08-04 16:42

MAX9376 LVDS/任意逻辑至LVPECL/LVDS、双路电平转换器 概述 The MAX9376 is a fully differential

2009-12-19 12:11

本篇主要介绍LVDS、CML、LVPECL三种最常用的差分逻辑电平之间的互连。 下面详细介绍第二部分:不同逻辑电平之间的互连。 1、LVPECL的互连 1.1、LVPECL到CML的连接 一般情况下

2020-12-20 11:49

双输出LVPECL晶体振荡器(Maxim) Maxim推出双输出LVPECL晶体振荡器DS4625,设计用于要求苛刻的通信系统。该器件产生两路100MHz至625MHz范围的高频输出,允许设计人员使用单

2009-11-02 08:57

本文采用CPLD和LCPECL门电路器件来设计可调窄脉冲发生器。本方案包括LVPECL窄脉冲产生电路和CPLD控制电路两部分,利用CPLD提供10 MHz的激励信号和对延时芯片进行写延时控制字来产生所需

2012-12-13 14:51