LVPECL(低压正射极耦合逻辑)是一种输入输出(I/O)技术,从半导体工艺无法集成高性能P 型设备与高性能N 型设备起就已出现。因此,在随后的HCSL 和LVDS等高速接口中,需要外部无源器件来完成由P 型设备完成的任务。

2018-05-28 10:44

LVPECL即Low Voltage Positive Emitter-Couple Logic,也就是低压正发射极耦合逻辑,使用3.3V或2.5V电源,LVPECL是由PECL演变而来的。

2017-04-26 10:16

MAX9375是一个高速、全差分、任意电平到LVPECL的转换器,设计信号速率高达2GHz。其极低的传输延迟和高速等特性,尤其适合于多种高速网络路由和背板应用。

2025-05-16 15:07

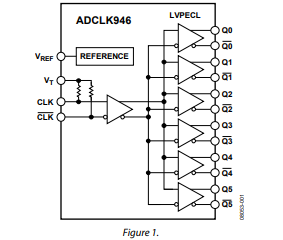

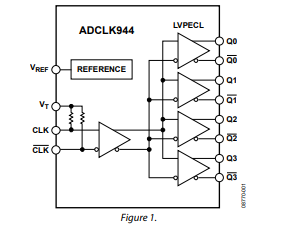

Ω片上端接电阻的差分输入。支持直流耦合LVPECL、CML和3.3 V CMOS(单端)和交流耦合1.8 V CMOS、LVDS和LVPECL输入。V~REF~引脚可用来为交流耦合输入提供偏置。

2025-04-11 10:31

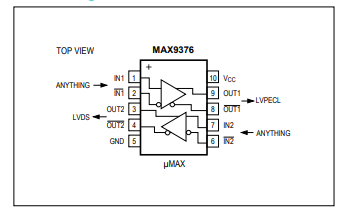

MAX9376是全差分、高速、LVDS/任何输入至LVPECL/LVDS双通道转换器,适用于高达2GHz的信号速率。一个通道是LVDS/任何输入至LVPECL转换器,另一个通道是LVDS/任何输入至LVDS转换器。MAX9376具有超低的传播延迟和高速度,因此非常

2025-05-16 14:57

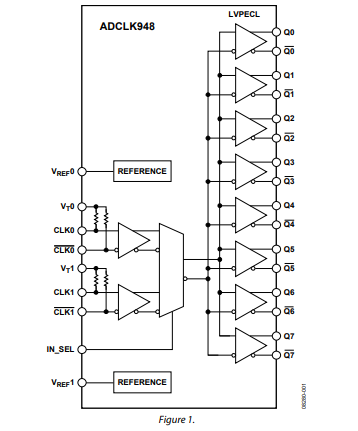

选择。两个输入均配备中心抽头、差分、100 Ω片内端接电阻,接受直流耦合LVPECL、CML、3.3 V CMOS(单端)以及交流耦合1.8 V CMOS、LVDS和LVPECL输入。提供V~REF~x引脚用于偏置交流耦合输入。

2025-04-11 09:30

, ZIN是接收器的输入阻抗。 PS:这里仅显示CMOS和PECL/LVPECL电路。 串行端接 实际上,因为阻抗会随频率动态变化,难以达到阻抗匹配,所以缓冲器输出端可以省去电阻(R)。 优势: 低功耗解决方案(没有对地的吸电流) 很容易计算R的值 R (Z0 ZOUT). 弱点

2019-11-11 15:55

Ω片内端接电阻的差分输入,支持直流耦合LVPECL、CML、3.3 V CMOS(单端)输入和交流耦合1.8 V CMOS、LVDS、LVPECL输入。 V~REF~ 引脚可用来为交流耦合输入提供偏置。

2025-04-10 16:23

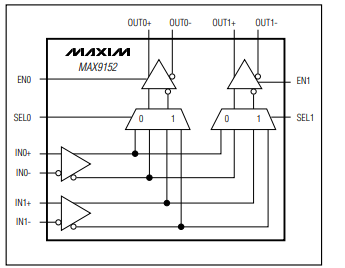

MAX9152 2 x 2交叉点开关专为需要高速、低功耗和低噪声信号分配的应用而设计。该器件包括两路LVDS/LVPECL输入、两路LVDS输出和两路用于设置差分输入和输出之间内部连接的逻辑输入。

2025-04-16 10:47

探索SN65LVCP23:2x2 LVPECL交叉点开关的卓越性能与应用 在电子工程师的设计工具箱中,高速、可靠的开关器件是实现复杂信号处理和传输的关键。今天,我们将深入探讨德州仪器(TI

2025-12-30 10:35