问候,两个与ODDR相关的问题:1)如果我想将由同一个BUFG驱动的同一时钟转发到多个外部设备,我是否必须实例化几个ODDR?或者,如果我只是实例化一个ODDR并将输出驱动到指向外部设备的多个

2018-11-02 11:28

今天用了PLL的IP核,但是提示要用ODDR2才能把输出的时钟信号输出到FPGA的普通IO口上,求大神指导,什么是ODDR2,怎么使用,还有就是怎么在ISE上查看它的接口?

2016-12-14 11:22

IDDR与ODDR的简述RGMII时序简述千兆网输入与输出模块的设计测试模块的设计仿真测试结果总结

2021-01-22 06:09

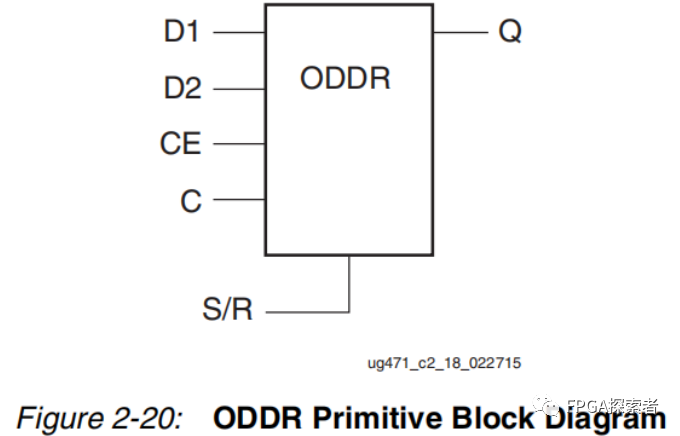

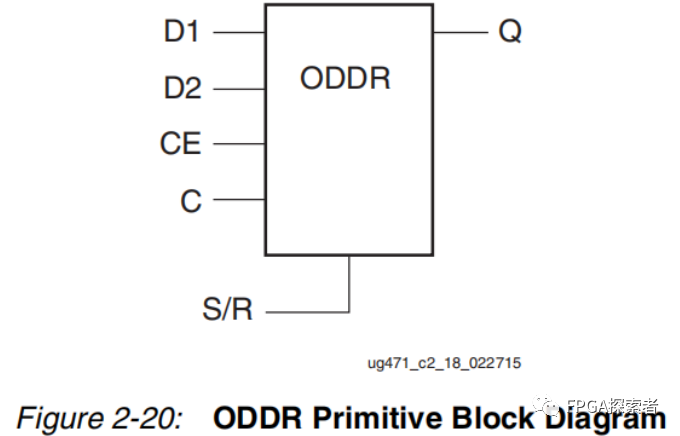

在SDR接口中,ODDR转发时钟(仍在时钟树内),输出端要直连到输出port,不可加逻辑,连接方式:输出时钟连接ODDR的C引脚,D1固定值1'b1, D2固定值1'b0,CE固定值1’b1,ODDR

2023-06-21 14:11

嗨,我附上了一个非常简单的ISE项目。我有一个2位自由运行计数器(cnt)指望clk的上升沿。 cnt输出定向到两个ODDR2实例的D0输入。 ODDR2的D1输入设置为“0”,C0设置为clk

2019-07-08 07:02

你好我将virtex5 LX50与具有应根据standardEIA / TIA-644 LVDS规范终止的输出数据的设备连接起来我在用着IBUFDS用于将输入LVDS转换为LVTTL,OBUFDS用于输出信号和时钟这是这样做的正确方法为此目的使用ODDR原语的重要性是什么?问候uzmeed

2020-06-17 14:59

在SDR接口中,ODDR转发时钟(仍在时钟树内),输出端要直连到输出port,不可加逻辑

2023-06-27 10:21

注意:ODDR与IDDR工作有一个复位时间,大概110-120ns之间 IDDR是上升沿采一次数据,下降沿采一次数据,形成的双路数据在下一个时钟沿输出。

2020-12-30 16:27

嗨,我复制在顶级模块中粘贴下面的ODDR代码,但它显示了一些错误。我可以知道我还应该做些什么吗?谢谢最好的祝福

2020-05-07 08:45

程序里,tx_data_oddr_s[l_inst]经OBUFDS输出两个正交的量,一路作为I(tx_data_out_p),一路作为Q(tx_data_out_n)进入AD9361输入引脚。应该是

2016-01-15 17:51