注意:ODDR与IDDR工作有一个复位时间,大概110-120ns之间 IDDR是上升沿采一次数据,下降沿采一次数据,形成的双路数据在下一个时钟沿输出。

2020-12-30 16:27

在数据的传输过程中,我们经常可以碰见双沿传输数据到FPGA,或者FPGA传输双沿数据给外部芯片,最常见的例子就是DDR芯片。这里说明一下,FPGA内部处理的数据都是单沿数据,那么双沿数据的变换只能发生在FPGA的IOB上面,这里有特定的硬件结构可以实验上面单沿变双沿的方法,也就是使用原语进行一些列的操作。

2021-01-25 07:07

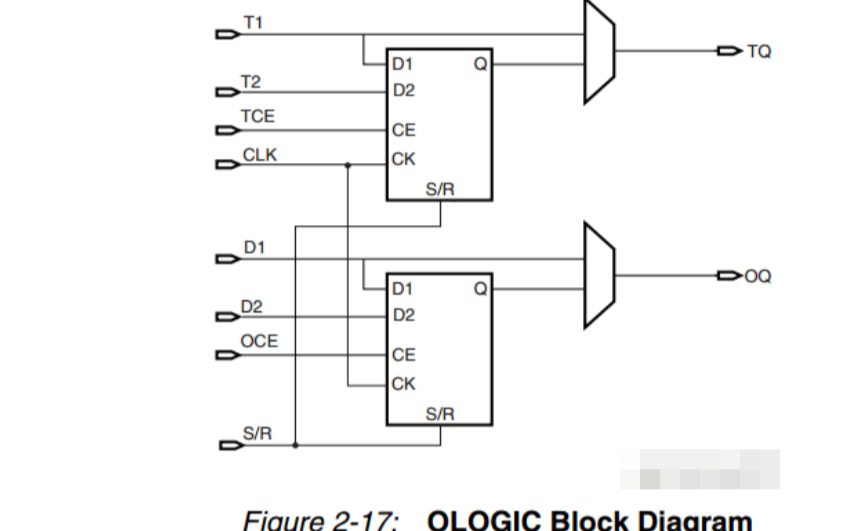

OLOGIC块在FPGA内的位置紧挨着IOB,其作用是FPGA通过IOB发送数据到器件外部的专用同步块。OLOGIC 资源的类型有OLOGIC2(位于HP I/O banks)和OLOGIC2(位于HR I/O banks)。在本文的下述论述中,除非特殊说明,OLOGIC2和OLOGIC3在功能和端口上都是相同的。

2020-12-30 16:27

,才发现输出的时钟信号完全没有反应!!是时钟的IO没有加ODDR,还是什么其他的原因?解释: 自己的这种想法完全是错的!!首先:不是所有的时钟都需要加上ODDR的!!! 在xilinx的FPGA中,要

2016-08-22 16:45