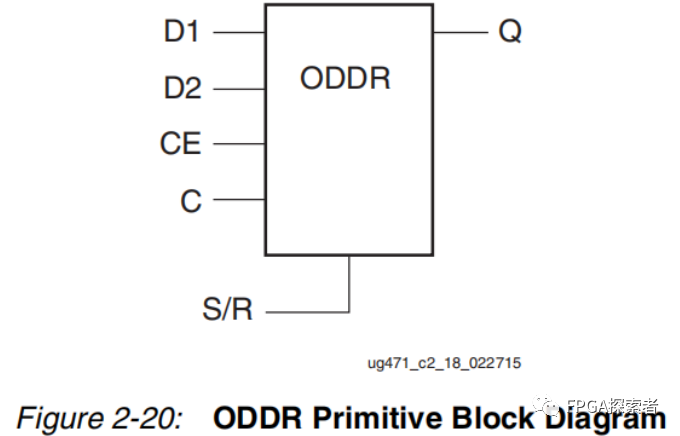

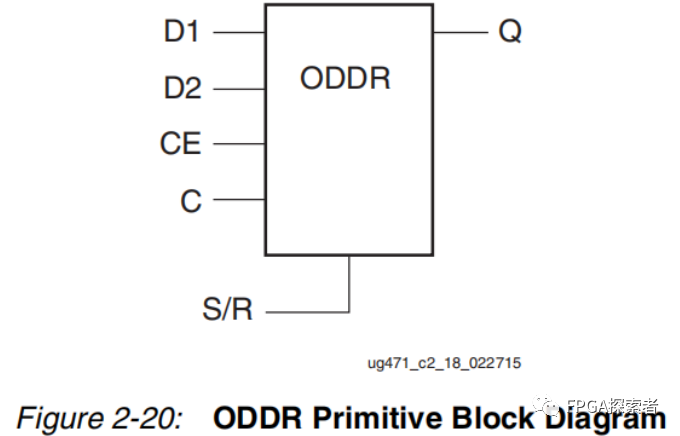

在SDR接口中,ODDR转发时钟(仍在时钟树内),输出端要直连到输出port,不可加逻辑,连接方式:输出时钟连接ODDR的C引脚,D1固定值1'b1, D2固定值1'b0,CE固定值1’b1,ODDR

2023-06-21 14:11

OLOGIC块在FPGA内的位置紧挨着IOB,其作用是FPGA通过IOB发送数据到器件外部的专用同步块。

2019-02-17 10:55

在SDR接口中,ODDR转发时钟(仍在时钟树内),输出端要直连到输出port,不可加逻辑

2023-06-27 10:21

idelay2中按推荐配置,从DATAIN还是从IDATAIN输入区别为是内部延时还是从IO输入,FIXED固定延时,idelay value先输入0,,时钟是200M,其他全部接0。

2020-11-25 14:35

1 IDDR 1.1 介绍 该设计元素是专用的输入寄存器,旨在将外部双数据速率(DDR)信号接收到Xilinx FPGA中。IDDR可用的模式可以在捕获数据的时间和时钟沿或在相同的时钟沿向FPGA架构显示数据。此功能使您可以避免其他时序复杂性和资源使用情况。 1)OPPOSITE_EDGE模式-以传统的DDR方法恢复数据。给定分别在引脚D和C上的DDR数据和时钟,在时钟C的每个上升沿之后Q1发生变化,在时钟C的每个下降沿之后Q2发生变化。 2)SAME_EDGE模式-时钟C的相对边沿仍然恢复数据。

2021-03-05 18:11

。使用lvds来接收高速ADC产生的数据会很方便。像ISERDES,IDDR,IDELAY,OSERDES,ODDR这种资源在FPGA的IOB中多得是(每个IO都对应有,最后具体介绍),根本不担心使用。

2018-06-30 10:23

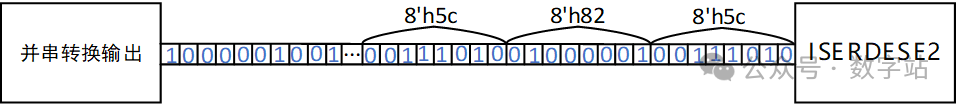

前面在讲解HDMI接口之前,讲解过IDDR、ODDR、OSERDESE2、IBUF等原语,之后一直有读者在问什么时候更新ISERDESE2这个原语。前文讲解过这些原语都在HDMI或者RGMII中使用过,但是ISERDESE2这个原语目前我的板子除了HDMI输入,其余并不会使用到,所以当时就没有出。

2025-03-17 10:52

/out_ddr_flop_spi_clk_i0/ODDR_inst/C] -divide_by 1 -invert [get_ports spi_clk_pin] 这里需要注意的是,如果该约束中使用get_pins(即产生的时钟并非输出到管脚),那么无

2020-11-17 16:28

,它是7系列FPGA新设计的IO专用FIFO,主要用于IOLOGIC(例如ISERDES、IDDR、OSERDES或ODDR)逻辑功能的扩展。 FPGA的每个BANK有4个IN_FIFO和4个

2020-11-29 10:08