电子发烧友

1.1w次浏览

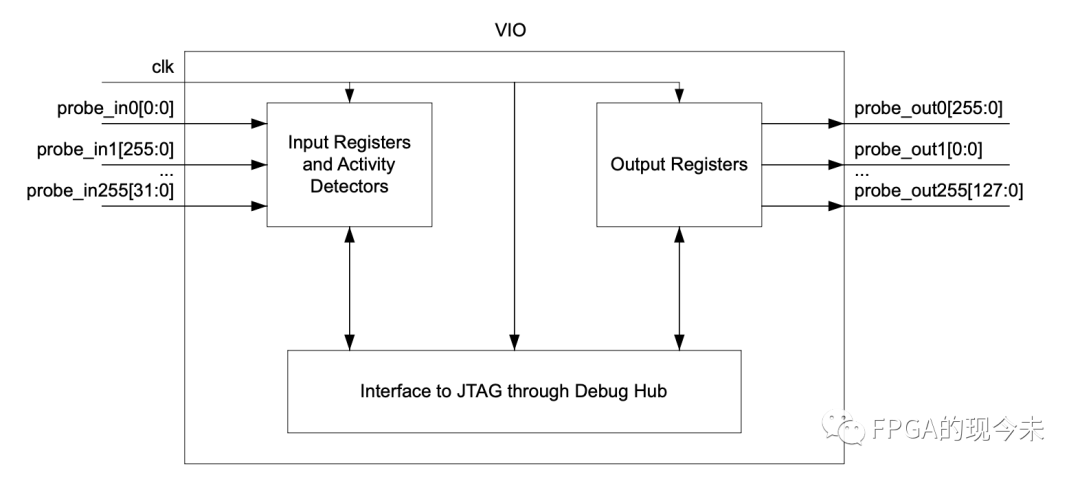

虚拟输入输出(Virtual Input Output,VIO)核是一个可定制的IP核,它可用于实时监视和驱动内部FPGA的信号,如图所示。 可以定制VIO的输入和输出端口的数量与宽度,用于

2021-09-23 16:11

一般情况下ILA和VIO都是用在chipscope上使用,VIO可以作为在chipscope时模拟IO。

2022-06-12 15:51

请问VIO输出的控制信号的类型该如何设置?如图有三种类型分别是什么意思

2019-04-27 15:50

只能识别一条Chain(User0)。所以,如果要同时在analyzer里面使用ILA(看波形)和VIO会不太现实(需要自己手动例化ILA Core和连接需要看的信号)。但是通过TCL可以访问所有

2012-03-08 15:29

电压比较器VIO的开环测试 输入失调电压(VIO)是电压比较器(以下简称比较器)一个重要的电性能参数,GB/T 6798-1996中,将其定义为“使输出电压为规定

2010-01-15 17:57

本帖最后由 神奇艾尔斯 于 2019-10-28 10:50 编辑 如题,我想写一个计数器,我设置一个值开始加,加到1000停止;count在always块里,是reg型,好像无法连到vio上

2019-10-28 09:57

在Vivado中,VIO(Virtual Input/Output)是一种用于调试和测试FPGA设计的IP核,它允许设计者通过JTAG接口实时读取和写入FPGA内部的寄存器,从而检查设计的运行状态并修改其行为。VIO IP核提供了一个简单易用的接口,使得用户可以轻

2025-06-09 09:32

在以往的项目中,要控制FPGA内部某个信号的值,往往是通过配置寄存器来实现的。其实Xilinx还提供了一个叫VIO的core,可以动态改变FPGA内部某个信号的值,但是一直没有用过,一来对于以前的项目来说,没有应用场景,通过寄存器就可以配置了;二来感觉这个东西不是很“实用”。

2023-12-11 18:26

AC3 7MM GROMMET VIO 100 PACK

2024-08-01 23:21