SystemC中的模块 模块(SC_MODULE)是SystemC系统建模的一个基本单位。一个系统由许多个模块构成,各个模块实现系统中不同的功能。在设计中,设计者需要根据功能把复杂的系统划分成若干个

2023-11-02 15:31

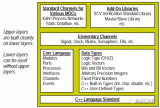

就 SystemC 和 SystemVerilog 这两种语言而言, SystemC 是C++在硬件支持方面的扩展,而 SystemVerilog 则继承了 Verilog,并对 Verilog 在面向对象和验证能力方面进行了扩展。这两种语言均支持

2010-08-16 10:52

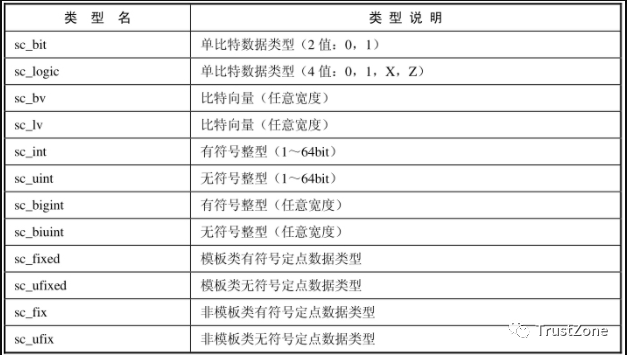

SystemC是基于C++的系统级设计语言,兼具描述硬件电路模型和面向对象的抽象能力。

2023-08-07 09:43

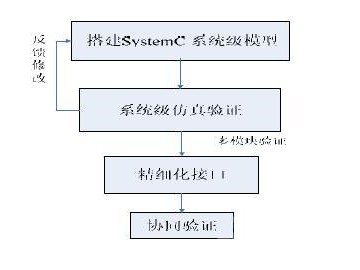

SystemC 是由C++衍生而来,本质是在C++的基础上添加了硬件扩展库和仿真核,这使SystemC 可以在不同抽象级对复杂电子系统建模。

2018-07-19 11:55

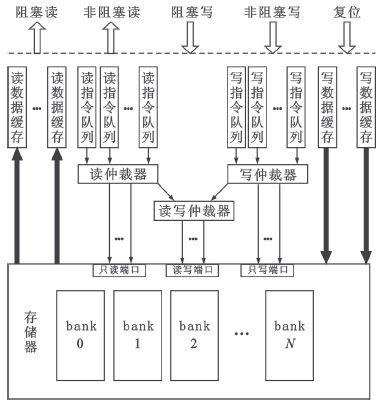

SystemC TLM中的接口 在SystemC TLM中,接口是一个C++的抽象类。抽象类中的所有方法都是用“=0”标识表示的纯虚函数。C++不允许创建抽象类的对象,因为抽象类对象是没有意义

2023-11-02 15:54

SystemC中的事件 在SystemC中,事件提供了一个底层的处理程序间同步及重新启动的方式,它能用来实现通道的功能,定义事件的语法如下: sc_event event_name; 另外,要触发或

2023-11-02 15:44

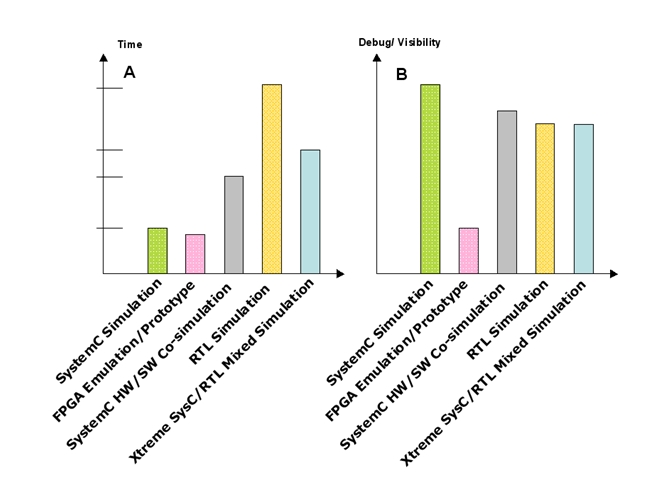

随着项目复杂程度的提高,最新的系统语言的聚合可以促进生产能力的激增,并为处在电子设计自动化(EDA)行业中的设计企业带来益处。SystemVerilog和SystemC这两种语言在设计流

2010-08-25 09:44

硬件建模。但是随着软硬件复杂度的提高,C/C++语言难以再满足要求。OSCI适时推出了SystemC语言来适应新的需求。如今SystemC已经被广泛应用于SoC软硬件建模中。

2018-12-05 07:43

支持SystemC的电子系统级(ESL)设计和验证环境旨在设计,分析,优化和验证片上系统(SoC)平台模型。这样的环境构成了已建立的RTL实现流程的前端。

2019-10-03 17:05

利用基于SystemC/TLM的方法学进行IP开发和FPGA建模 随着系统级芯片技术的出现,设计规模正变得越来越大,因而变得非常复杂,同时上市时间也变得更加苛刻。通常RTL已

2010-01-04 13:11