支持SystemC的电子系统级(ESL)设计和验证环境旨在设计,分析,优化和验证片上系统(SoC)平台模型。这样的环境构成了已建立的RTL实现流程的前端。

2019-10-03 17:05

本设计致力于用SystemC语言建立JESD024B的协议标准模型,描述JESD204B的所有行为,并且能够保证用户可以通过该JESD204B的SystemC库,进行JESD204B行为的仿真

2017-11-17 09:36

基于前面对DMA控制器工作流程的详细分析。运用SystemC 语言,建立DMA控制器的Cye le-Accurat级参考模型。控制器由以下几个模块组成:寄存器赋值、状态转换。输出模块和顶层模块。具体工作过程可以参考如图3所示的有限状态机

2017-12-07 16:21

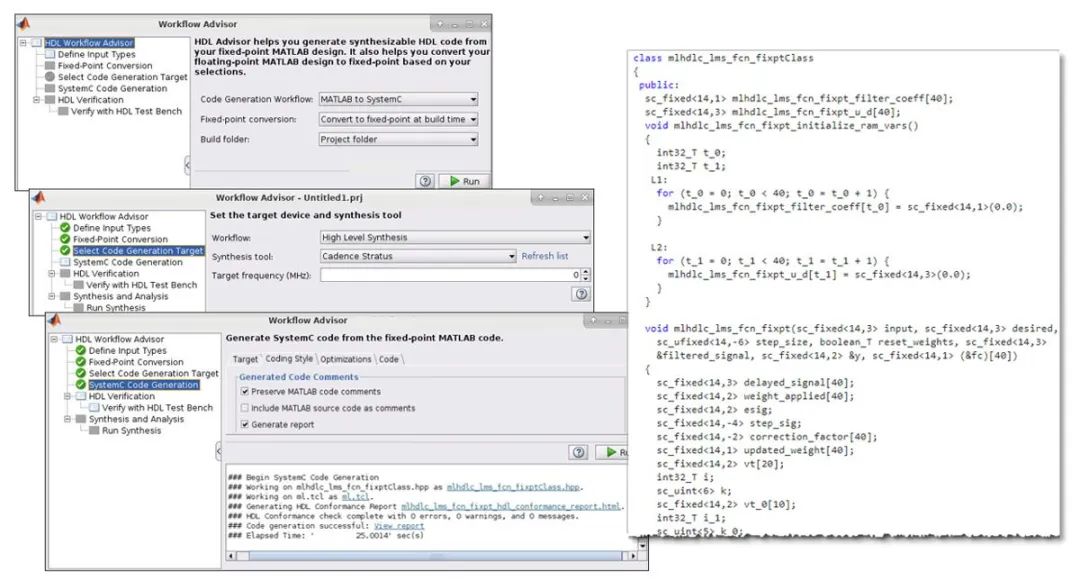

ASIC 设计是开发复杂电子系统的过程。该系统可制造成特殊用途的半导体设备,通常用于大批量应用或具有严格的功耗、性能和尺寸限制的应用。ASIC 系统设计人员使用高级语言并通过仿真和可视化来开发和评估算法。

2023-07-20 10:29

AMD Vivado 设计套件以文件和库的形式提供仿真模型。仿真库包含器件和 IP 的行为和时序模型。编译后的库可供多个设计项目使用。用户必须在设计仿真之前通过名为 compile_simlib 的实用程序编译这些文件,以便为目标仿真器编译仿真模型。

2025-12-12 15:08

虽然 SystemC/C++ 编程风格已使用多年,但最近出现了一些特定使用模式,它们推动工程团队采用共同的设计流程。这包括抽象算法设计代码用作高层次综合 (HLS) 工具的输入,虚拟平台模型用于早期软件测试,可配置的知识产权 (IP) 模块,等等。

2025-06-24 11:07

当FPGA开发者需要做RTL和C/C++联合仿真的时候,一些常用的方法包括使用MicroBlaze软核,或者使用QEMU仿真ZYNQ的PS部分。

2023-12-13 10:13

通过建模不仅可以对芯片的性能做出分析,还可以在硬件没有完成之前开发软件,不仅提高了产品成功率,而且缩短了研发周期。设计人员早期采用C/C++语言进行硬件建模。

2014-08-21 18:14

当FPGA开发者需要做RTL和C/C++联合仿真的时候,一些常用的方法包括使用MicroBlaze软核,或者使用QEMU仿真ZYNQ的PS部分。

2023-12-13 10:11

Vivado HLS 是 Xilinx 提供的一个工具,是 Vivado Design Suite 的一部分,能把基于 C 的设计 (C、C++ 或 SystemC)转换成在 Xilinx 全可编程芯片上实现用的 RTL 设计文件 (VHDL/Verilog 或 Syst

2018-06-05 10:31