SerDes是一种功能块,用于对高速芯片间通信中使用的数字化数据进行序列化和反序列化。用于高性能计算(HPC)、人工智能(AI)、汽车、移动和物联网(IoT)应用的现代片上系统(SoC)都实现了

2025-03-27 16:18

首先我们要了解什么是SerDes,SerDes的应用场景又是什么呢?SerDes又有哪些常见的种类?

2023-06-06 17:03

SERDES的优势 引脚数量和通道优势 SERDES最明显的优势是具备更少的引脚数量和线缆/通道数量。对于早期的SERDES,这意味着数据可以通过同轴电缆或光纤发送。 对于现代的

2021-07-23 11:59

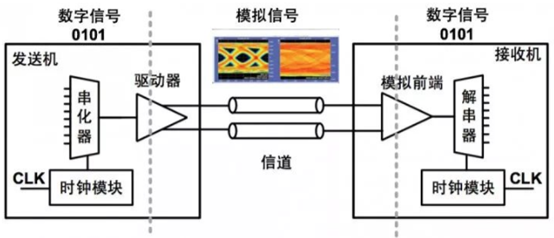

SERDES是英文SERializer(串行器)/DESerializer(解串器)的简称。

2024-01-04 09:04

尽管设计和验证很复杂,SERDES 已成为 SoC 模块不可或缺的一部分。随着 SERDES IP 模块现已推出,它有助于缓解任何成本、风险和上市时间问题。

2023-10-23 14:44

SerDes 是空间到时间到空间的转换。并行数据同时传输但占用不同的物理互连,串行数据共享相同的物理空间但占用不同的时间时刻

2023-01-31 14:13

FPGA发展到今天,SerDes(Serializer-Deserializer)基本上是器件的标配了。从PCI发展到PCI-E,从ATA发展到SATA,从并行ADC接口到JESD204,从RIO到

2023-10-16 14:50

SerDes是SERializer(串行器)/DESerializer(解串器)的简称,是一种主流的时分多路复用(TDM)、点对点(P2P)的串行通信技术。

2023-11-14 09:32

FPGA发展到今天,SerDes(Serializer-Deserializer)基本上是标配了。

2022-10-31 11:28

我们知道,SERDES对参考时钟有严格的相位噪声性能要求。通常,SERDES供应商会根据其SERDES采用的PLL以及CDR架构特点,以及性能数据,提出对参考时钟的相位噪声的具体要求。

2017-02-10 18:40