LOCK_PINS 是 Xilinx Vivado 做物理约束的属性之一。用来将LUT的逻辑输入(I0,,I1,I2...)绑定到其物理输入pin上(A6,A5,A4...)。

2023-01-11 10:52

要用到,CLOCK_DEDICATED_ROUTE偶尔能够应应急。而这里要介绍的LOCK_PINS,笔者至今没有碰过,估计大家在实践中恐怕也很难有机会或必要用上它。但谁知道呢?存在即是合理,相信

2022-11-28 15:24

Stratix III FPGAs support SGMII GigE operation on LVDS I/O pins at 1.25 Gbps. With Stratix III

2018-06-22 01:16

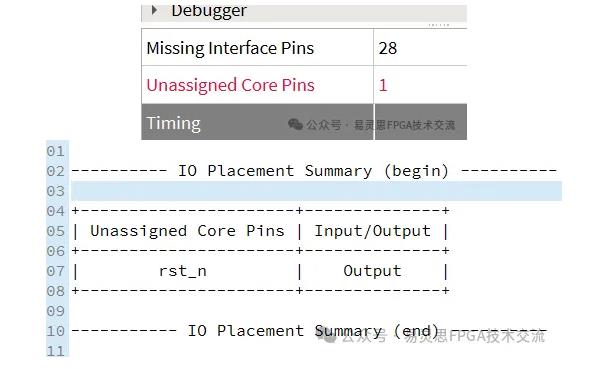

接上篇: (6)查看Unassigned Core Pins。 在placement下面的palce.rpt文件中搜索 Unassigned C ore Pins就可以看到。它说明这些管脚没有用于内部连接。 大家可以点击这个链接查看上文 Efinity编译生成文件

2024-08-13 14:22

: create_generated_clock -name clk_samp -source [get_pins clk_gen_i0/clk_core_i0/clk_tx] -divide_by 32 [get_pins

2020-11-17 16:28

一、建立原点座标:(用PADS 2005 打开没有layout BGA文件)1.鼠标右键,点选"Select Traces/Pins",再点BGA的左上角的一

2010-06-24 17:49

Include Unassigned Pins:含义是扇出的时候,将没有网络的管脚也进行扇出,一般不用勾选,空网络的管脚不用进行扇出

2020-05-01 11:28

。 这样会在xdc中自动生成如下约束: set_false_path -from [get_clocks -of_objects [get_pins clk_gen_i0/clk_core_i0

2020-11-14 11:28

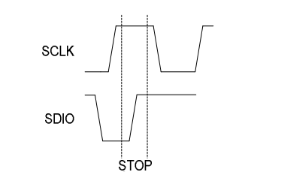

关于 Bit Bang 的解释:Use software to control serial communication at general-purpose I/O pins,简单来讲就是使用软件通过 IO 脚去实现 I2C 的时序从而使用 I2C 协议进行通信。

2017-11-06 09:32

to drive both individual LED digits and shared segment pins. This application note details what steps must be taken to map t

2010-03-17 09:05