MDIO接口,是Management Data Input/Output的缩写。MDIO接口包含在IEEE802.3协议中,是专用于以太PHY的管理的串行总线接口。

2020-09-29 14:55

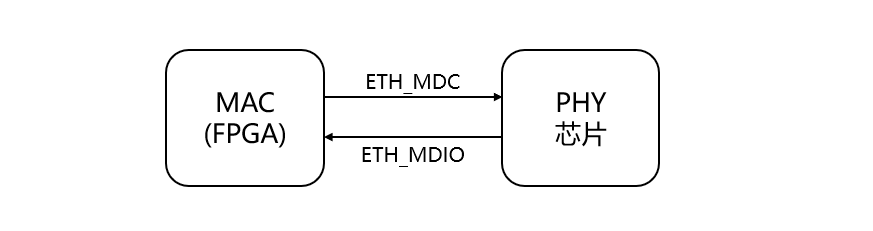

一个管理接口,这个管理接口通常称为 MDIO,MIIM 或者 SMI。 这个接口用于 MAC 从 PHY 读取相关管理寄存器的值,或者往 PHY 管理寄存器上写入数据。

2023-01-26 16:02

本文开源一个FPGA项目:MDIO接口读写测试。以太网通信模块主要由 MAC (Media Access Control)控制器和物理层接口 PHY (Physical Layer)两部分构成。其中

2023-10-01 09:46

MDIO主机(即产生MDC时钟的设备)通常被称为STA(Station Management Entity),而MDIO从机通常被称为MMD(MDIO Management Device)。通常STA都是MAC层器件

2024-02-27 09:32

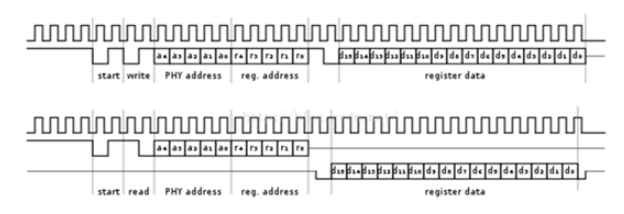

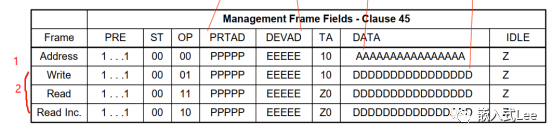

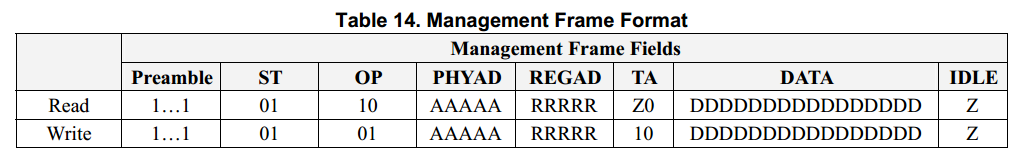

MDIO 也支持 Clause 45 时序,其是 Clause 22 的拓展协议。与 Clause 22 不同的是, 16 位中的起始位:Clause 22 是 00, 而 Clause 45 是 01.

2020-10-07 15:25

本文转自公众号欢迎关注 基于DWC_ether_qos的以太网驱动开发-MDIO驱动编写与测试 一.前言 以太网驱动的编写与调试往往从MDIO接口开始,MDIO是MAC访问PHY的接口。实现通过

2023-08-30 09:37

无法破解。不同厂家之间无法移植,而且为了通用性考虑牺牲了效率,因此自己动手写一个以太网MAC是个不错的选择。 本博文讨论通过MDIO接口管理PHY芯片来验证其正确工作,为在此基础上设计MAC逻辑开个头。PHY芯片采用RTL8211EGVB,选用GMII接口与MAC连接

2020-12-29 14:17

在设计中,通常总是优先处理光口、PCIE等高速信号、或者是音频等模拟信号。规划使用最优的层,最优的通道,阻抗、延时、串扰等细节也被优化到极致。然而剩下的低速信号往往不被重视。

2019-04-24 09:33

本文主要介绍以太网的MAC(Media Access Control,即媒体访问控制子层协议)和PHY(物理层)之间的MII(Media Independent Interface ,媒体独立接口),以及MII的各种衍生版本——GMII、SGMII、RMII、RGMII等。

2023-07-26 11:48

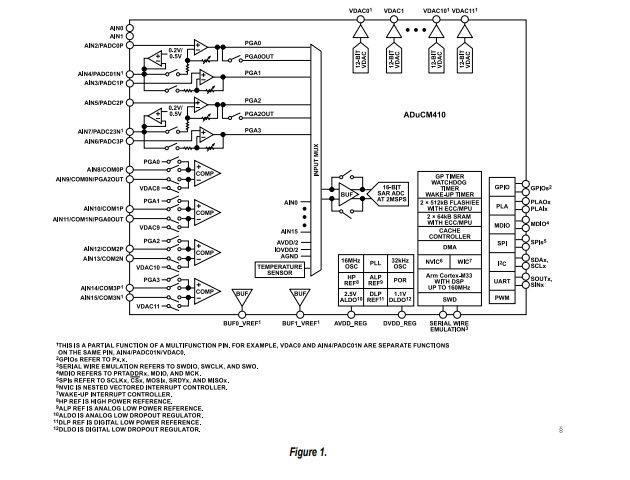

ADuCM410 是一款完全集成的单封装套件,包括高性能模拟外设套件和数字外设套件(由 160MHz Arm^®^ Cortex ^™^ -M33 处理器控制)以及用于数字码和数据的集成闪存。

2025-05-08 11:14