一个管理接口,这个管理接口通常称为 MDIO,MIIM 或者 SMI。 这个接口用于 MAC 从 PHY 读取相关管理寄存器的值,或者往 PHY 管理寄存器上写入数据。

2023-01-26 16:02

在设计中,通常总是优先处理光口、PCIE等高速信号、或者是音频等模拟信号。规划使用最优的层,最优的通道,阻抗、延时、串扰等细节也被优化到极致。然而剩下的低速信号往往不被重视。

2019-04-24 09:33

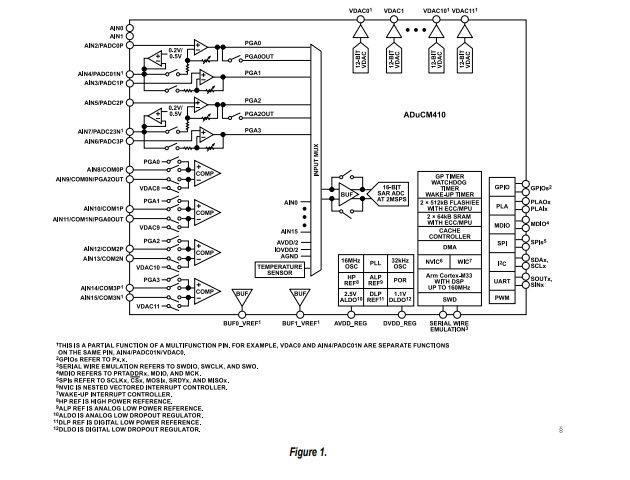

ADuCM410 是一款完全集成的单封装套件,包括高性能模拟外设套件和数字外设套件(由 160MHz Arm^®^ Cortex ^™^ -M33 处理器控制)以及用于数字码和数据的集成闪存。

2025-05-08 11:14

ADuCM420 是一款完全集成的单封装套件,包括高性能模拟外设套件和数字外设套件(由 160MHz Arm ^®^ Cortex ^™^ -M33 处理器控制)以及用于数字码和数据的集成闪存。

2025-05-08 11:06

下面详细介绍了6个功能模块及其应用特点:并行接口、串行接口、时钟分布电路、8B/10B编解码电路、PRBS测试以及相关寄存器访问控制接口MDIO。

2021-06-26 16:10

PHY芯片为OSI的最底层-物理层(Physical Layer),通过MII/GMII/RMII/SGMII/XGMII等多种媒体独立接口(介质无关接口)与数据链路层的MAC芯片相连,并通过MDIO接口实现对PHY状态的监控、配置和管理。

2023-07-26 11:46

PHY芯片为OSI的最底层-物理层(Physical Layer),通过MII/GMII/RMII/SGMII/XGMII等多种媒体独立接口(介质无关接口)与数据链路层的MAC芯片相连,并通过MDIO接口实现对PHY状态的监控、配置和管理。

2023-05-04 10:06

今天讲解是RGMII的FPGA设计。因为这边文章主要是用XILINX的约束工具,所以标记为XILINX,其实你用altera平台也可以的。设计分为2部分,一部分讲解MDIO操作和IEE802.3寄存器要求。另外一部分主要讲解PHY层的软件设计。

2018-07-02 04:41

逻辑信号,反之亦然。 器件理想用于漏极开路I²C总线和MDIO总线,具有三态输出模式(/TS)。将/TS上拉至I/O口电源,置于逻辑高电平,从而在关闭电平转换功能时支持供电侧的连续、不间断I²C的工作。MAX14611采用TDFN封装,是MAX3378E引脚兼容的升级版本。

2025-05-15 15:22