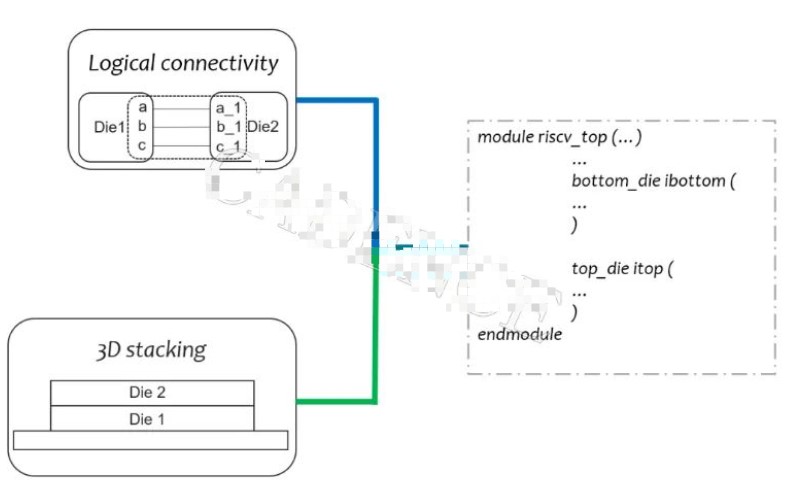

提供了一系列三维堆叠设计流程,通过将二维芯片网表分解成双层的三维堆叠结构,用户可以探索三维堆叠裸片系统相对于传统二维设计的性能优势,改善内存延迟,实现性能突破。

2022-09-06 14:19

Cadence Integrity 3D-IC 平台是业界首个全面的整体 3D-IC 设计规划、实现和分析平台,以全系统的视角,对芯片的性能、功耗和面积 (PPA) 进行系统驱动的优化,并对 3D-IC 应用的中介层、封装和印刷电路板进行协同设计。

2022-05-23 16:52

信号完整性仿真大多针对由芯片IO、传输线以及可能存在的接插件和分立元件所构成的信号网络系统,为了实现精确的仿真,仿真模型的精确性是首先需要保证的。一般情况下,Allegro PCB SI会执行传输线和分立元件的建模,而芯片IO和连接器的模型通常会由原厂提供。

2018-08-04 10:01

对于大规模的芯片设计,自上而下是三维集成电路的一种常见设计流程。在三维布局中,可以将原始二维布局中相距较远的模块放到上下两层芯片中,从而在垂直方向相连,减少模块之间的线网长度。

2022-08-03 13:51

本文介绍Cadence Tempus电源完整性解决方案如何为燧原科技(Enflame)面向数据中心而开发的先进节点人工智能(AI)芯片提供电源完整性(Power Integrity, PI)和信号完整性(Signal Integrity, SI)保障。

2023-07-12 11:12

Integrity 3D-IC 平台具有强大的数据管理功能,能够实现跨团队的一键数据同步与更新。同时,Integrity 3D-IC 支持灵活的 3D-IC 实现流程,配合其高效的数据管理机制,可以让用户在流程中的多个关键阶段接入内嵌的分析平台,进而实现整个系统的

2022-07-19 09:34

高速设计研究的范畴也是广义SI的研究对象,具体可以分为三个部分:信号完整性(Signal Integrity, SI)、电源完整性(Power Integrity, PI)以及电磁兼容

2019-04-20 11:02

PI(Power Integrity),即电源完整性,以前隶属于信号完整性分析专题,但是因为PI足够复杂和关键,现在已经把其单独拿出来作为一个专题去研究。

2018-06-15 10:19

在设计高速高密度PCB时,串扰(crosstalk interference)确实是要特别注意的,因为它对时序(timing)与信号完整性(signal integrity)有很大的影响。以下提供几个注意的地方。

2018-01-17 15:04

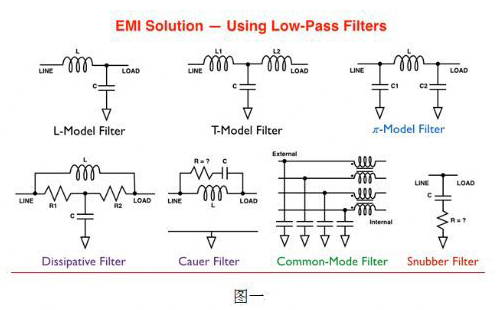

要解决这些烦人的电磁干扰问题,首先从大的方向来分类,可分为信号完整性(SI, Signal Integrity)的问题,以及电源完整性(PI, Power Integrity)的问题。在实务的测量

2019-08-16 17:38