一、gicv2与gicv3 但是在gicv3之前一直都是使用的giv2,这两者有什么区别? 最近在做实验室的版本兼容,很我一直以为这个gicv2和

2023-11-07 17:54

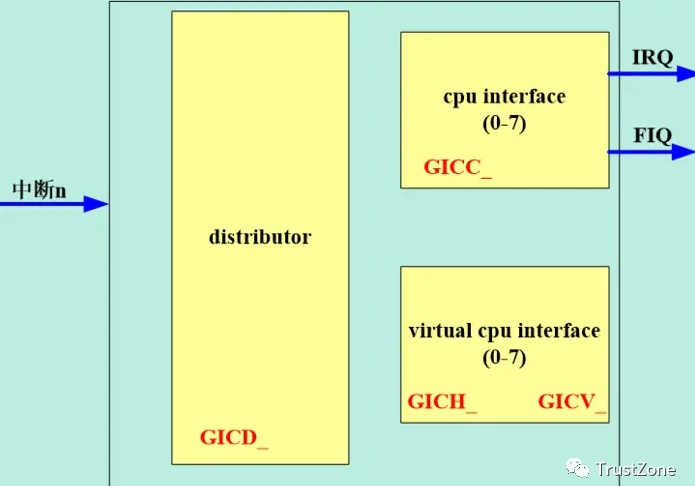

(1)gicv2的寄存器 gicv2寄存器,都是使用memory-mapped的方式去访问的 • ◾GICD_: distributor的寄存器 • ◾GICH_: 虚拟interface的控制

2023-11-08 16:09

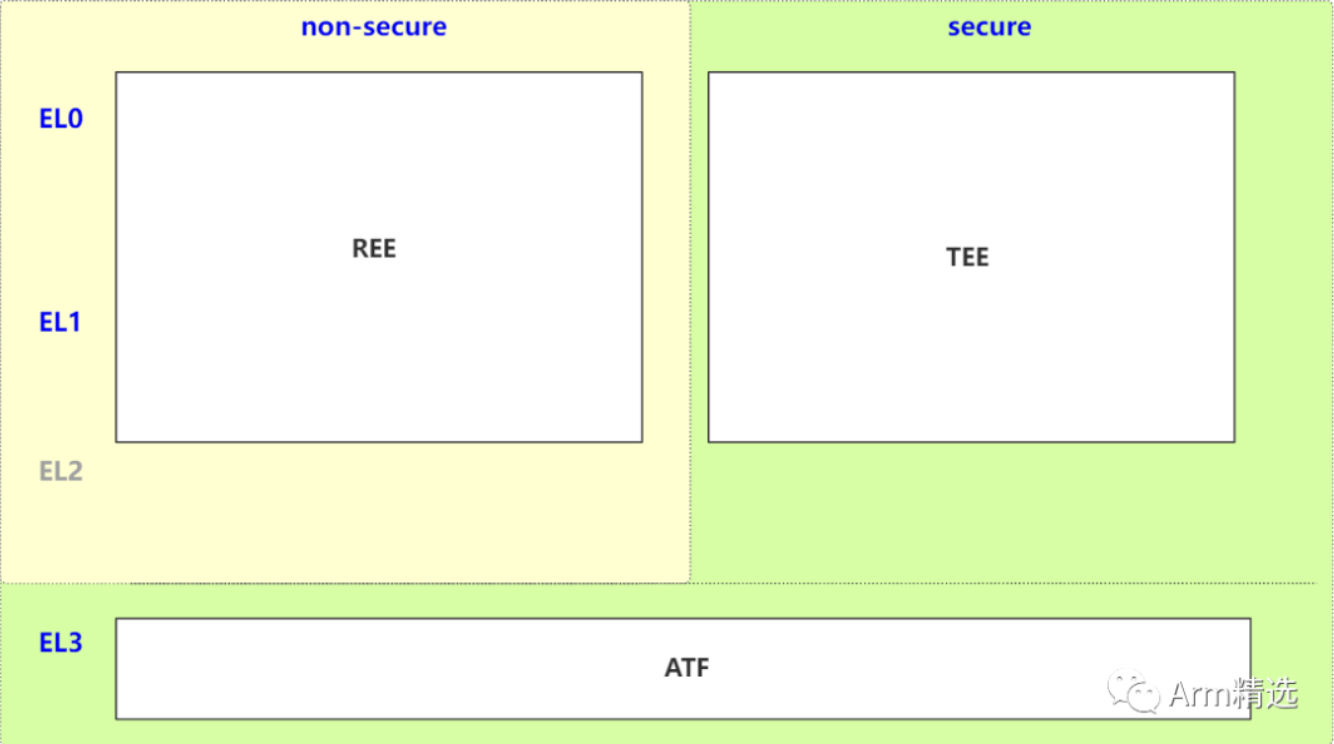

中断控制器以gicv3/gicv4为例,不讨论其它中断控制器和gicv2。

2023-09-01 17:31

(1)gicv2和ARM Core的连接 ARM cortex-A系列处理器,提供了4个管脚给soc,实现外界中断的传递 • ◾nIRQ:物理普通中断 • ◾nFIQ: 物理快速中断

2023-11-07 18:07

在默认情况下,本文讲述的都是ARMV8-aarch64架构,gicv3, linux kernel 5.14

2024-08-07 09:29

(1)gicv2的组件 在GICv2中,最大支持8个core • distributor:实现中断分发,对于PPI,SGI是各个core独有的中断,不参与目的core的仲裁,SPI是所有core共享

2023-11-08 15:57

MPSoC是带ARM处理器和FPGA(PL)的SoC,包含4核A53及其常用外部模块(PS)。A53(PS)使用Arm GIC-400,属于GICv2架构。如果想了解GIC-400的具体细节,请

2022-08-02 09:14

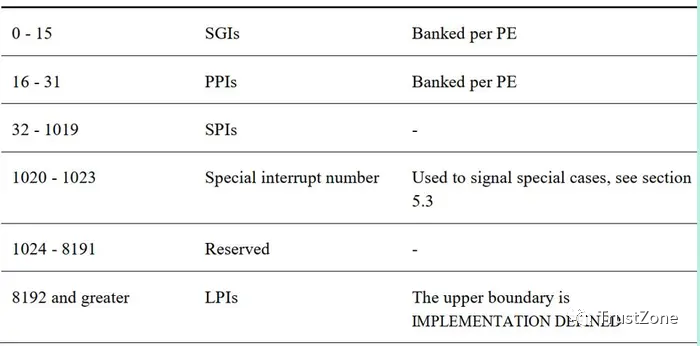

2-中断类型(红色是gicv2特有) • ◾PPI:(private peripheral interrupt),私有外设中断,该中断来源于外设,但是该中断只对指定的core有效。 • ◾SPI

2023-11-07 18:01

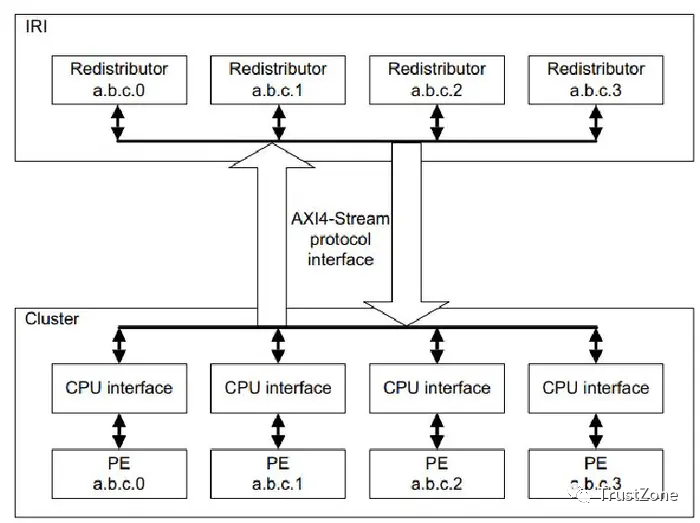

。 当前GIC 有四个版本,GIC v1~v4, 本文主要介绍GIC v3控制器。 GIC v3中断类别 GICv3定义了以下中断类型: SGI(Software Generated

2022-07-08 09:34

ARM处理器和FPGA(PL)的SoC,包含4核A53及其常用外部模块(PS)。A53(PS)使用Arm GIC-400,属于GICv2架构。如果想了解GIC-400的具体细节,请参考文档APU

2021-05-07 15:34