由于各种逻辑电平的输入、输出电平标准不一致,所需的输入电流、输出驱动电流也不同,为了使不同逻辑电平能够安全、可靠地连接,逻辑电平匹配将是电路设计中必须考虑的问题。

2022-11-10 10:01

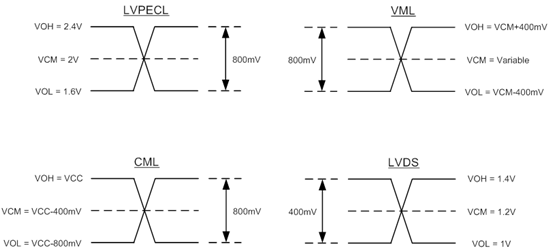

CML(Current-mode llogic)它并没有一个标准,是基于简单的差分放大器,如图2所示。通常取R1=R2=50欧姆,|VOUT+ - VOUT-| = R1 * i1 = 50*i1

2017-11-10 14:49

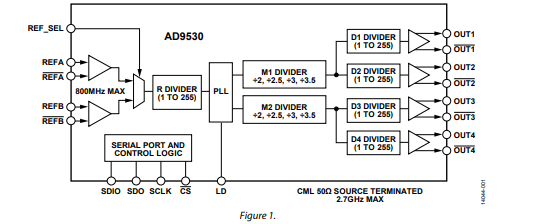

AD9530是一款针对40 Gbps/ 100 Gbps OTN应用的完全集成式PLL和分配器件,支持时钟清零和频率转换。 内部PLL可锁定至两个参考频率之一以生成最高达2.7 GHz的四个离散输出频率。

2025-04-10 09:16

系统当前包含 CML 与 LVDS 等各种接口标准。理解如何正确耦合和端接串行数据通道或时钟通道的传输线路是一项非常重要的技能。

2022-01-28 09:33

OmniClock系列支持从8 kHz到200 MHz的任意输出频率,有三个单端时钟输出(LVCMOS/LVTTL),两者可以组合成一个差分输出(LVPECL、LVDS、HCSL / CML),令设计人员可替代多个晶体和/或振荡器,降低整体系统成本。

2016-07-07 13:49

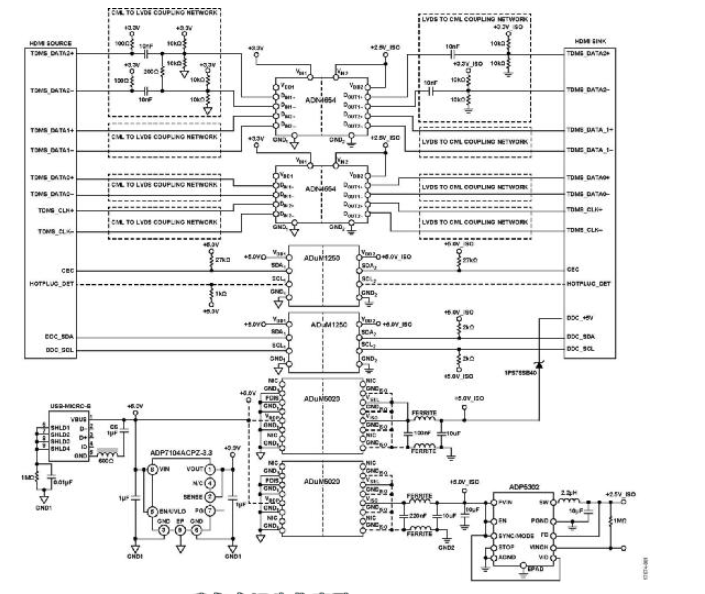

目前存在多个HDMI标准。图1所示电路符合1.3a版HDMI标准的要求。图1包含高速、转最小化传输差分信号(TMDS)时钟和数据线,它们通过物理层上的电流模式逻辑(CML)实施。

2019-09-23 14:37

。宽频带、全差分信号通路使累积抖动、串扰及信号偏斜最小。每路2 x 2矩阵开关能够扇出和/或复用高达2.7Gbps的数据和2.7GHz时钟信号。所有输入和输出与电流模式逻辑(CML)兼容,易于与交流耦合

2025-04-16 10:53

本示例描述了垂直锗硅光电探测器完整的器件级多物理(光学、电学)仿真,并生成集成模型用于INTERCONNECT进行光电链路仿真。案例还提供了一个自动化的工作流,用于自动运行器件级仿真并为CML Compiler收集数据以生成集成模型。在本例中计算得到了暗电流和光电流、响应度、带宽和眼图等关键结果。

2022-09-21 10:43

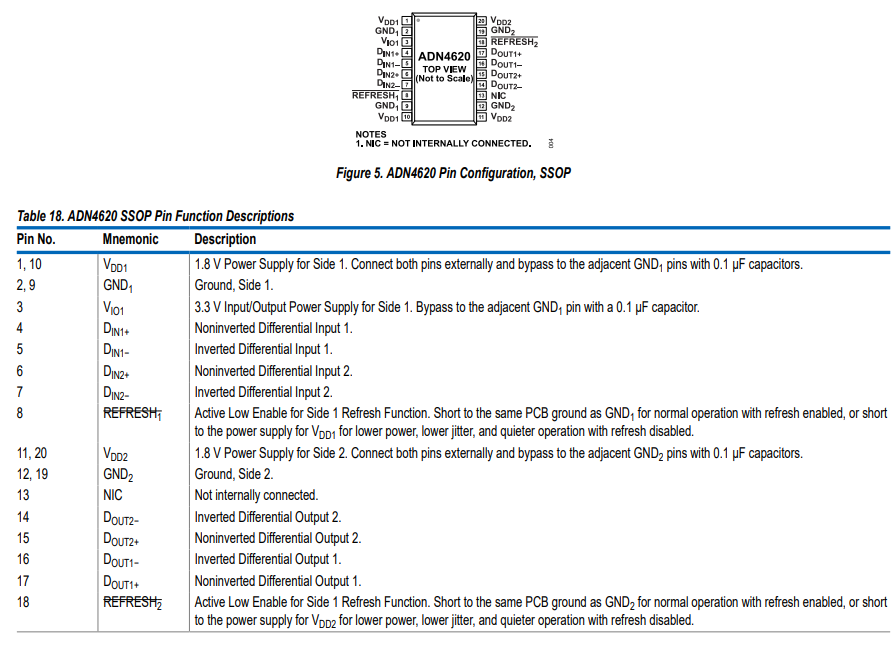

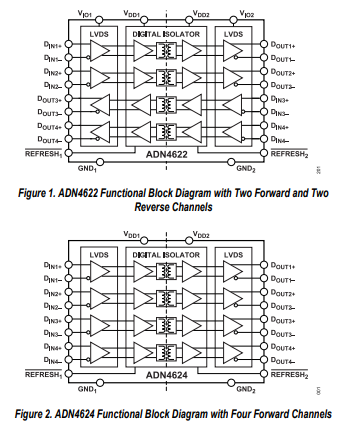

高速运行进行了增强,可提供LVDS信号链的插入式电气隔离。与LVDS接收器和LVDS驱动器之间的交流耦合和/或电平转换允许隔离其他高速信号,例如电流模式逻辑(CML)。

2025-05-29 14:42

*Coupler^®^ 技术,已针对高速运行进行增强,可提供 LVDS 信号链的插入式电气隔离。到 LVDS 接收器和来自 LVDS 驱动器的交流耦合和/或电平转换允许隔离其他高速信号,例如电流模式逻辑 (CML)。

2025-05-29 14:37