什么是 CLB?CLB 将一个经优化的高速可编程逻辑集成到 C2000 MCU 等实时控制器中,为增强型脉宽调制器 (PWM)、增强型捕捉、增强型正交编码器和通用 I/O 等关键外设提供智能的信号输入/输出 (I/O) 路由功能,最终成为具有系统级差异化特性的增强

2021-12-07 14:59

CLB可配置逻辑块是指实现各种逻辑功能的电路,是xilinx基本逻辑单元。下图给出了一个 SLICEM 的内部结构。

2022-10-08 09:43

CLB是xilinx基本逻辑单元,每个CLB包含两个slices,每个slices由4个(A,B,C,D)6输入LUT和8个寄存器组成。

2022-04-24 14:48

本视频介绍了7系列CLB架构,包括:LUT,触发器,专用多路复用器,进位链和其他资源。

2018-11-27 06:39

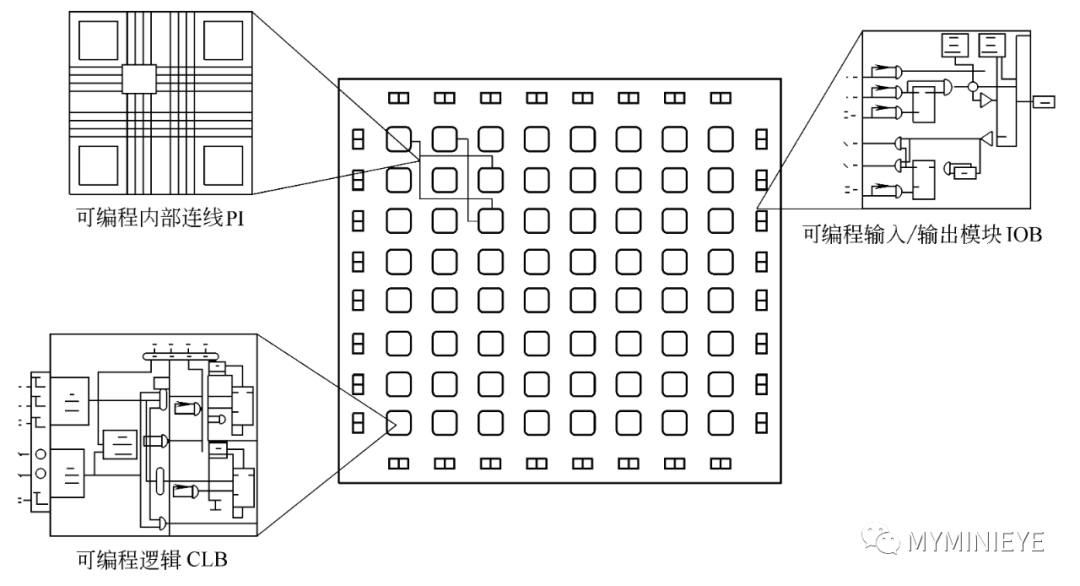

现在的FPGA里面有很多存储资源,DSP(数字信号处理)资源,布线通道,I/O资源,当然最根本的还是CLB(Configurable Logic Block)。Xilinx的资源分布采用ASMBL架构。

2018-10-22 11:00

7系列FPGA是Xilinx新推出的基于28nm工艺的FPGA,其中包含三个系列:Artix、Kintex和Virtex。因项目要使用kintex7为平台做设计,需要对其内部结构做了研究,首先从CLB(Configurable Logic Block)开始

2017-02-10 16:13

CLB是指可编程逻辑功能块(Configurable Logic Blocks),顾名思义就是可编程的数字逻辑电路。CLB是FPGA内的三个基本逻辑单元。CLB的实际数量和特性会依器件的不同而

2020-11-02 17:18

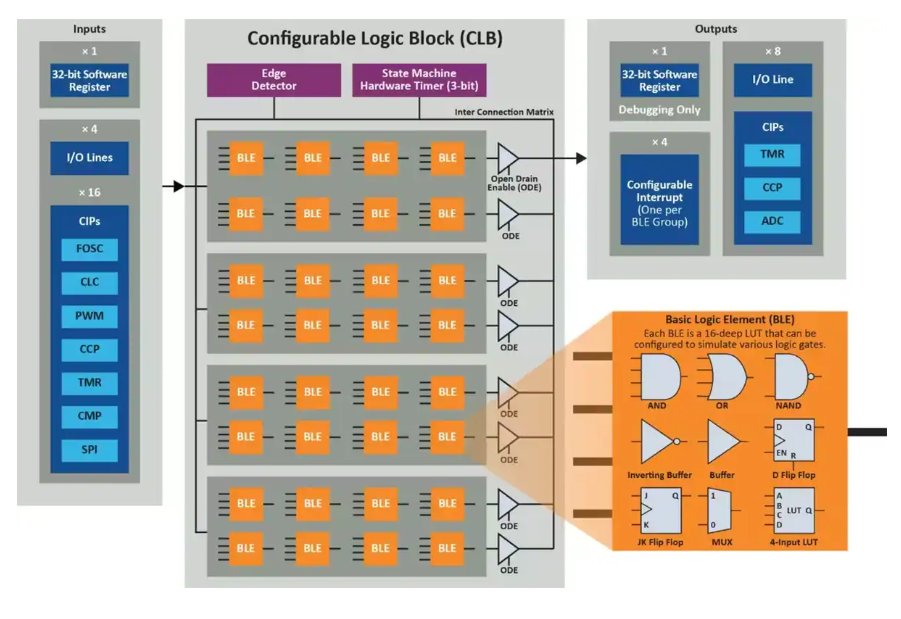

Microchip Technology PIC16F13145 CLB微控制器为具有一组专用外设、基于硬件的设计提供了高效的解决方案。 Microchip Technology

2025-10-09 16:05

LUT中文名字叫查找表。以7系列的FPGA为例,每一个Slice里面有四个LUT。FPGA就是通过LUT实现大量的组合逻辑,以及SLICEM里面的LUT还可以构成RAM,Shift Register,以及Multiplexers。这篇文章我们一起来学习LUT如何构成组合逻辑。

2023-03-13 10:28

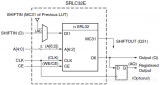

一、移位寄存器 SLICEM函数发生器也可以配置为32位移位寄存器,而无需使用slice中可用的触发器。以这种方式使用,每个LUT可以将串行数据延迟1到32个时钟周期。 移入D(DI1 LUT引脚)和移出Q31(MC31 LUT引脚)线路将LUT级联,以形成更大的移位寄存器。因此,SLICEM中的四个LUT被级联以产生高达128个时钟周期的延迟。也可以在多个SLICEM上组合移位寄存器。 寄存器,LUT B / C / D的MC31输出也不可用。由此产生的可编程延迟可用于平衡数据流水线的时序。 下图是S

2025-01-16 17:45