随着行业发展,对降低PPM和提高直通率要求的不断提高,以上方式暴露出许多问题,无法满足品质管控要求。比如更换钢网厂家是否完全理解设计要求,需要较长的磨合期;企业花大力气积累的工艺设计数据无法有效保护;长期合作的钢网厂家,由于对接人员变动等因素,钢网设计品质波动较大。

2018-05-09 15:45

:工欲善其事,必先利其器。所以问题不在工程师,关键在于他们手上缺乏好工具。行业痛点正是我们攻关的目标,望友 Vayo-Stencil Designer 钢网数字化设计软件方案,不仅颠覆了传统钢网设计到

2021-07-01 13:46

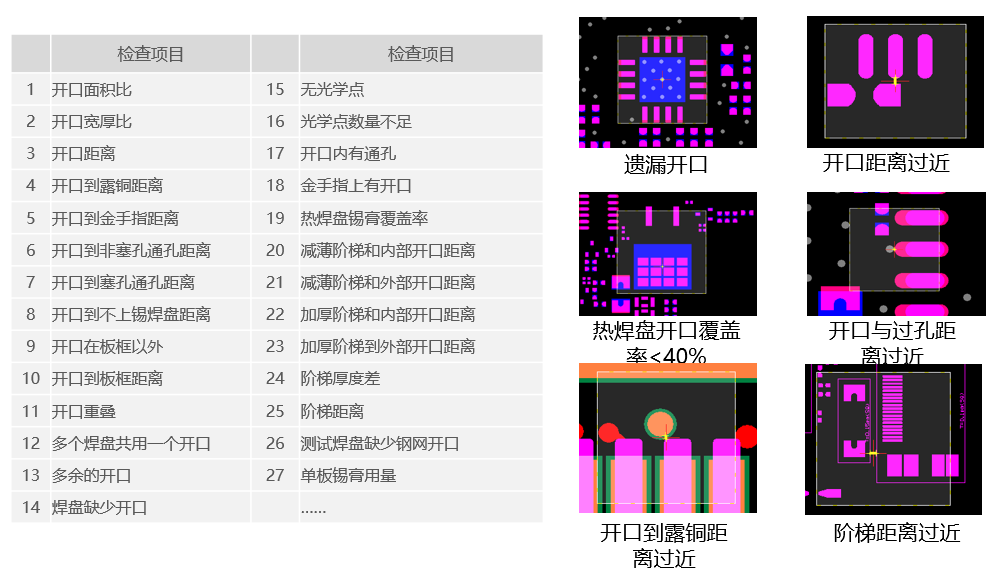

软件介绍 Vayo-Stencil Designer Vayo-Stencil Designer(简称VSD)是一款面向企业的专业钢网设计软件,可以为企业高效构建适合企业自身产品和工艺

2023-06-02 13:27

Land Pattern and Solder Stencil

2021-02-19 11:48

Land Pattern and Solder Stencil

2021-02-19 11:47

1.数据源支持,Vayo-CAM365 软件,支持以下类型数据:(1)Gerber(RS-274-X;RS-274-D)(2)Drill(3)DXF(4)PCB CAD(IPC-2581;ODB++

2021-09-23 14:34

4.智能测量,操作步骤:1)导入数据源 Gerber(或者ODB++/IPC-2581);2)左下方层列表中隐藏不需要的层,显示焊盘层; 图13)在工具栏选择“元件\对象”模式; 图24)按下鼠标左键框选焊盘,选中测量对象; 图3点击右键,选择“查看距离”; 图4 图55. 智能捕捉器件中心坐标,操作步骤:1)导入数据源 Gerber(或者ODB++/IPC-2581);2)左下方层列表中隐藏不需要的层,显示焊盘层;图63)在工具栏选择“元件\对象”模式; 图74)按下鼠标左键框选器件焊盘,选中器件; 图8点击鼠标右键,选择“查看坐标”; 图9 图106.高效版本比较与报告输出操作步骤:1)导入数据源 Gerber(或者ODB++/IPC-2581);2)菜单栏点击“实用工具\工程比较”; 图11提示保存工程,选择“是”,保存后弹出以下窗口: 图123)在B工程路径栏导入待比较的数据,把需要比对的层拖动到左边窗口“B工程的层”下方对应层位置,如下图红框所示,详见文末操作视频; 图134)勾选需要比较的层,点击上图“对比”按钮,自动生成对比报告; 图14视频讲解如下链接:https://mp.weixin.qq.com/s?__biz=Mzg3MzYxODM0Mg==&mid=2247493214&idx=1&sn=1c4d3bdc7a2961d0f4ca5ef73198f53d&chksm=cedfe897f9a861815999d259f1738430d06457b8c0c45c94a4de3667ee2fc505b75852298e46&token=1089890750&lang=zh_CN#rd

2021-09-28 13:46

1.读读入孔层文件; 图一Vayo-Gerber View 读入 Drill 层2.选显示孔层,隐藏其它层,点击孔,即可选中; 图二Vayo-Gerber View 已选定的孔,高亮显示3.看左上角

2022-01-24 14:56

lntel Xeon Phi协处理器的指令集IMCI引入了硬件实现的vgather指令,旨在帮助512位SIMD寄存器访问非连续内存地址上的数据。然而实验结果显示,vgather很有可能成为应用在Xeon Phi协处理器上关键的性能瓶颈之一。基于以上结论,针对vgather的性能建模可以帮助用户深入地掌握和理解Xeon Phi协处理器的性能特性。在实验方法上,本文方法与现存的通过程序段内嵌入汇编代码进行数据统计不同,使用PAPI等性能分析工具直接收集硬件计数器的统计结果,作为模型的实验

2017-11-25 10:50

ICT relies on good contact between the test probe and test pad. On OSP boards, it is important that the stencil allows solder paste to be applied to testpoi

2019-09-24 08:50