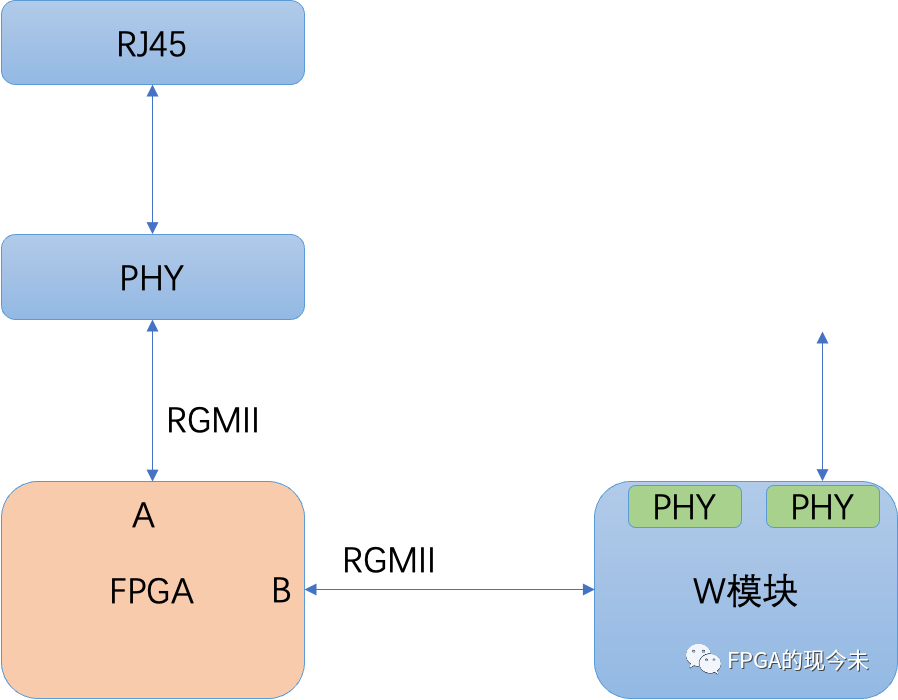

RGMII接口,是Reduced Gigabit Media Independent Interface的缩写。IEEE802.3 Clause 35在RS子层和PCS子层之间定义了一组接口GMII,该接口作为MAC和PHY数据交互接口。

2020-09-30 11:26

本案例描述了一个由于CPU和PHY之间RGMII时序不满要求导致通信异常问题,最后通过电感材料(磁珠)对信号相位的移位特性来改变信号延时,从而解决RGMII信号延时不够的案例,实验结果通过。

2024-01-05 09:47

RGMII接口是双沿采样时钟,数据位宽为4bit,而GMII接口是单沿采样时钟,数据位宽是8bit。

2023-06-09 11:23

ZynqZU+ Mpsoc的以太网使用普遍,从功能大致分为2类应用:调试管理、数据传输。本文主要集中在PS端的Ethernet RGMII外接phy设计和调试,该部分客户用的最多也最容易出问题,希望

2021-09-29 10:47

今天讲解是RGMII的FPGA设计。因为这边文章主要是用XILINX的约束工具,所以标记为XILINX,其实你用altera平台也可以的。设计分为2部分,一部分讲解MDIO操作和IEE802.3寄存器要求。另外一部分主要讲解PHY层的软件设计。

2018-07-02 04:41

RGMII接口是MAC和PHY之间常用的千兆网通信接口,采用4bit数据接口,工作时钟为125Mhz,并且上升沿和下降沿同时传输数据,因此传输速率可达1000Mbps。

2023-08-30 10:10

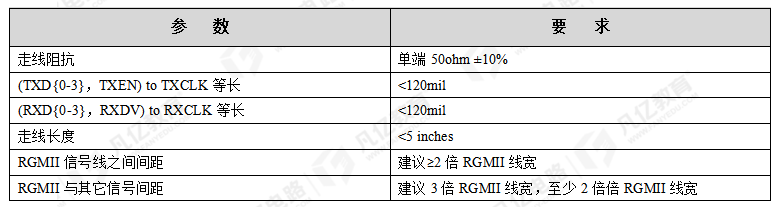

最近项目中,FPGA通过多个RGMII接口与其他设备通信,在通信的过程中,有一个RGMII接口对端设备始终无法驱动,最后通过共享一个PHY,时分复用的形式来“解决”该问题

2023-11-27 16:47

RGMII接口,是ReducedGigabitMediaIndependentInterface的缩写。IEEE802.3Clause35在RS子层和PCS子层之间定义了一组接口GMII,该接口作为MAC和PHY数据交互接口。

2020-12-14 10:23

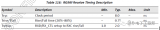

1 接口定义 RGMII 由 GMII (Gigabit Media Independent Interface) 简化演变而来,意为 Reduced GMII,是常见的以太网 MAC 和 PHY

2024-12-30 09:55

网络设备一定离不开MAC和PHY,有MAC和PHY的地方就有相应的接口,无论看得见或者看不见,它就在那里,不悲不喜。在以太网中,这个接口就是介质无关接口,英文称为Media Independent Interface,简称MII。MII适用于百兆网络设备,有个很大的缺点就是走线很多,于是就出现了RMII,即Reduced Media Independent Interface,在MII的基础上减少了一半的数据线。

2019-06-22 09:51