本案例描述了一个由于CPU和PHY之间RGMII时序不满要求导致通信异常问题,最后通过电感材料(磁珠)对信号相位的移位特性来改变信号延时,从而解决RGMII信号延时不够的案例,实验结果通过。

2024-01-05 09:47

今天讲解是RGMII的FPGA设计。因为这边文章主要是用XILINX的约束工具,所以标记为XILINX,其实你用altera平台也可以的。设计分为2部分,一部分讲解MDIO操作和IEE802.3寄存器要求。另外一部分主要讲解PHY层的软件设计。

2018-07-02 04:41

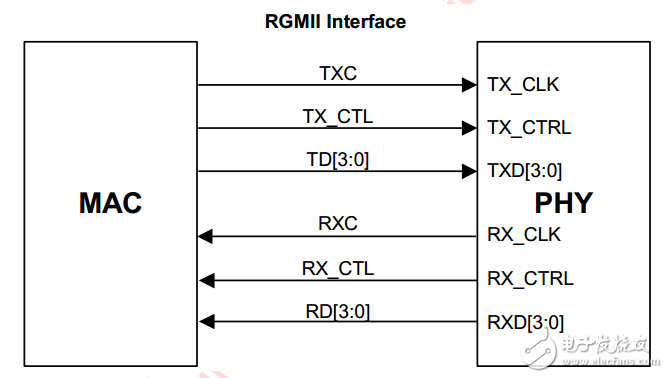

网络设备一定离不开MAC和PHY,有MAC和PHY的地方就有相应的接口,无论看得见或者看不见,它就在那里,不悲不喜。在以太网中,这个接口就是介质无关接口,英文称为Media Independent Interface,简称MII。MII适用于百兆网络设备,有个很大的缺点就是走线很多,于是就出现了RMII,即Reduced Media Independent Interface,在MII的基础上减少了一半的数据线。

2019-06-22 09:51

网络通信中的PHY芯片接口种类有很多,之前接触过GMII接口的PHY芯片RTL8211EG。但GMII接口数量较多,本文使用RGMII接口的88E1512搭建网络通信系统。这类接口总线位宽小,可以降低电路成本,在实际项目中应用更广泛。

2019-05-18 09:39

ARM端配置如下图所示,以5处的ARM-A9为核心,使用1处的UART1打印调试信息,使用2处的网口0进行以太网通信,使用3处的AXI GP(General Port)Master通用主设备接口连接PL端的AXI GPIO

2023-10-16 16:43

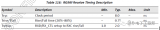

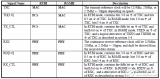

本文主要介绍以太网的MAC(Media Access Control,即媒体访问控制子层协议)和PHY(物理层)之间的MII(Media Independent Interface ,媒体独立接口),以及MII的各种衍生版本——GMII、SGMII、RMII、RGMII等。

2023-04-28 09:43

之前使用I.MX6Q/I.MX6Q(imx_3.0.35_4.1.0), 1GB RGMII 以太网测试性能大概 495Mbits/sec, 如下是iperf测试过程。

2022-11-09 10:48

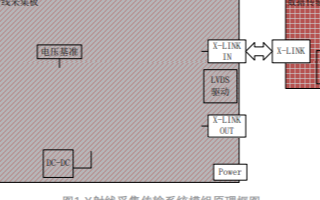

本文设计的X射线采集传输系统的硬件框图如图1所示。图像采集与传输系统的硬件包含三个部分,X射线探测器模块、FPGA数据采集模块和千兆以太网RGMII数据传输模块。

2020-07-14 17:24

Dual-core Cortex-A7 up to 1.0GHz Mali-400MP GPU DDR3/DDR3L 1080P H265/H264 BT.709 USB 2.0 HDMI 1.4 with HDCP 1.3 Audio DAC/CVBS/RGMII

2019-10-24 16:50

encoder TS in/CSA 2.0 USB 2.0 HDMI 1.4 with HDCP 1.3 Audio DAC/CVBS/RGMII

2019-10-25 11:18