Zynq MPSoC是Zynq-7000 SoC(之后简称Zynq)的进化版本。Zynq是赛灵思发布的集成PL(FPGA)和PS设计的最早的一代产品。如图2.1所示,在

2022-08-15 09:16

在ps的控制下,可以实现安全或非安全的配置所有ps和pl。通过zynq提供的JTAG接口,用户可以在外部主机的控制下对zynq进行配置,zynq不支持最开始就配置pl的过程。

2019-05-15 11:41

普通的 FPGA 一般是可以从 flash 启动,或者被动加载,但是ZYNQ不行,ZYNQ必须PS端参与

2022-07-22 10:10

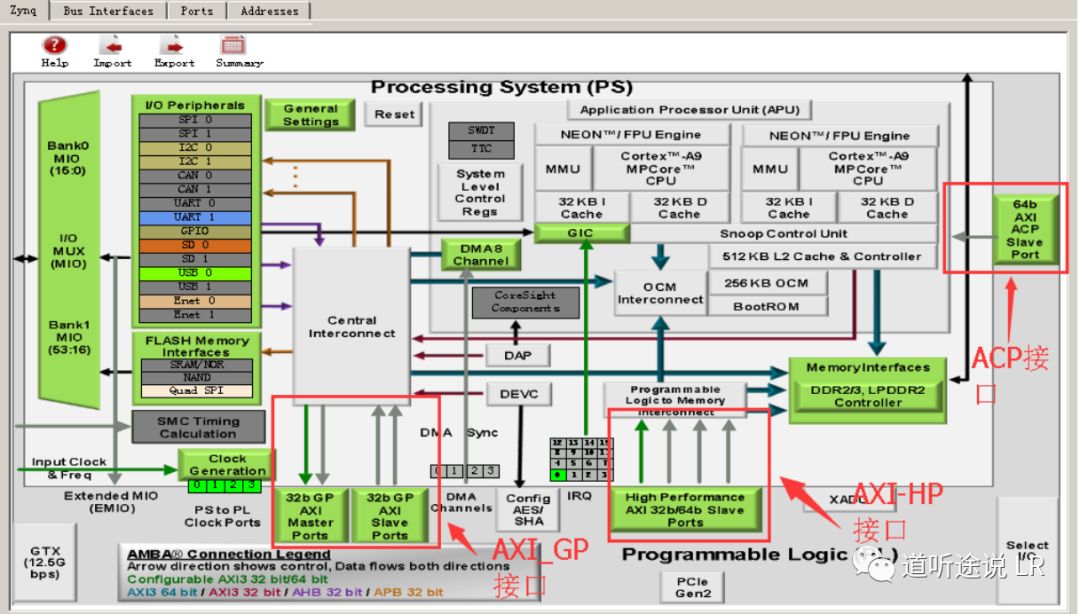

ZYNQ内部的总体框架如所示,PS中包含2个ARM Cortex-9的内核,一些基本的外设扩展口以及Memory接口。PS和PL的相互通信通过两个通路完成,分别是GP(General Purpose)Ports和HP(High Performance)Ports。

2023-09-22 09:26

目前OLED的驱动大部分都是基于STM系列ARM芯片和传统FPGA芯片。为适应Xilinx最新平台Zynq的人机交互需要,提出一种基于Zynq的OLED驱动设计方法。##Zynq的开发板

2014-09-04 16:16

Zynq 系列的亮点在于 FPGA 里包含了完整的 ARM 处理子系统(PS),每一颗 Zynq 系列的处理器都包含了Cortex-A9处理器,整个处理器的搭建都以处理器为中心, 而且处理器子系统

2023-08-06 10:20

本文试图搞清楚在 Xilinx 基于 ARM 的 Zynq-7000、Zynq UltraScale+ MPSoC 和 Zynq UltraScale+ RFSoC 器件中是否存在任何漏洞。

2018-06-28 15:53

通过这篇有趣的教程,熟悉运行在赛灵思 Zynq UltraScale+ MPSoC 上的 Xen 管理程序。 赛灵思和 DornerWorks 的系统软件团队在赛灵思的 Zynq

2017-11-18 18:39

任何一个嵌入式系统级的设计都离不开中断,对于拥有双cotex-A9的Zynq来说也一样。Zynq的中断设计由ARM与GIC pl390中断控制器组成,用于接收IOP(I/O peripherals

2017-11-22 08:10

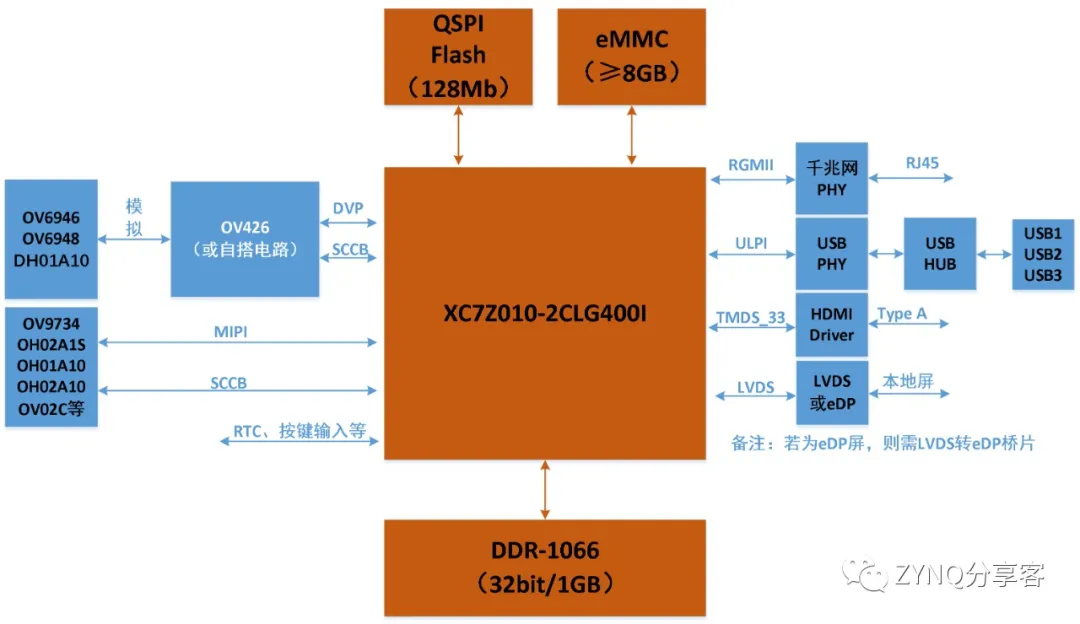

这一次,熊猫君分享一个内窥镜的技术实现方案。内窥镜的方案很多:主处理器有用专用ASIC的,比如日、台、韩的相机ASIC;有用专用CPU的,比如海思、瑞星微和君正等。熊猫君的这个是基于Xilinx ZYNQ的低成本方案。

2022-08-02 10:21