如果说TMS320C6678与Kintex-7进行搭配的DSP+FPGA架构堪称经典中的经典,那么TMS320C6678 与ZYNQ进行搭配的DSP+ARM+FPGA架构则为正在崛起的新势力!

2020-12-03 11:56

本白皮书探讨了TMS320C6678处理器的VLFFT演示。通过内置8个固定和浮点DSP内核的TMS320C6678处理器来执行16K-1024K的一维单精度浮点FFT算法样本,检测其分别在采用

2018-01-31 22:58

创龙结合TI KeyStone系列多核架构TMS320C6678及Xilinx Kintex-7系列FPGA设计的TL6678F-EasyEVM开发板是一款DSP+FPGA高速大数据采集处理平台,其

2020-02-12 13:42

址的组合,这个值会有所不同。表4列出了在1GHz C6678 EVM(64-bit 1333MTS DDR)上测得的从EDMA触发(写ESR)最小数据传输(1 word)到EDMA 传输结束(读到IPR=1) 的平均的时钟周期数。

2018-02-19 01:11

对于多核DSP应用技术来说,BootLoad技术是一个关键点,也是应用难点之一。针对8核高性能DSP——TMS320C6678的根配置问题进行了研究,包括上电加载过程,单核和多核的emif

2014-03-26 11:14

粒子群优化(Particle Swarm Optimization,PSO)算法[1]是由KENNEDY J和EBERHART R C等开发的一种新的进化算法。相对于遗传算法[2]等,该算法参数较少、容易实现,能够解决复杂的优化问题,因此在众多优化问题领域都得到了广泛的应用[3],如控制决策、目标跟踪、深度学习等。然而,粒子群优化算法在实际应用中往往难以达到实时性的要求,特别是求解复杂的多维问题时,速度问题更加突出,难以满足实际应用的需求。

2018-06-22 14:53

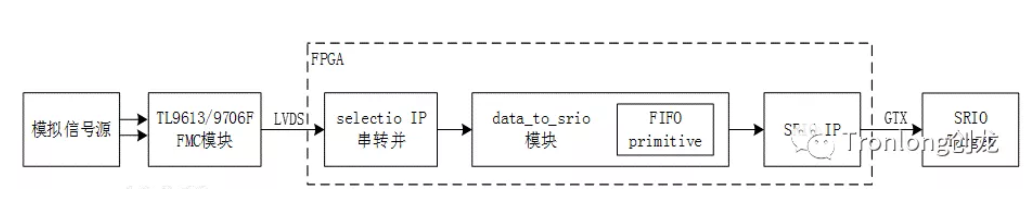

发送,因此数据量为16bit * 2 * 250M = 8Gbps; 2. AD数据通过SRIO由Kintex-7发送到C6678 DSP(Target)的0x0C3F0000~0x0C3F7FFF

2020-06-15 18:18

本文为您分享基于C66x+FPGA的SRIO开发视频教程,适用于创龙TMS320C6678、TMS320C665x、Kintex-7、Artix-7平台。

2020-07-01 10:47

在Kintex-7 FPGA上搭建MicroBlaze软核,并由MicroBlaze配置PAL视频模块TL2867F和各IP核,将模块输出的一路4通道D1时分复用的复合视频,拆分成4路独立的BT656嵌入式同步视频,再将4路视频进行BT656解码分离出同步信号和像素数据。

2020-11-27 17:01

对于两个长度不同的特征向量,很难衡量它们的相似性。因此,作者提出了一种特殊的度量,中心核对齐(CKA),整个论文中都在使用这个。假设X和Y是m个不同样本的特征矩阵,K=XX^T^, L=YY^T^,则利用Hilbert-Schmidt独立准则(HSIC)的定义,定义CKA如下:

2022-09-08 10:37