Integrator/LM-XCV400+逻辑模块被设计为开发用于ARM内核的ASB、AHB和APB外设的平台。 您可以通过三种方式使用它: ·作为独立系统,具有基准电源·具有集成器核心模块和集成

2023-08-12 07:44

Apex FPGA。积分器/LM-XCV60OE+配备了Xilinx Virtex E现场可编程门阵列。 逻辑模块的功能由上电时加载到现场可编程门阵列的配置映像定义。 闪存中预加载了两个FPGA配置

2023-08-12 07:59

两维图像相关跟踪是空间太阳望远镜1m光学系统达到0.1“分辨率关键之一。介绍了基于FPGA实现SST相关算法的方法,如2×2矢量基蝶形FFT、模块化结构、两级状态机、动态块浮点、并行流水时序等.20MHz下32×32图像相关算法在XCV800芯片上实现仅713 微秒,像元拟合精度优于1/50.

2021-03-11 16:07

两维图像相关跟踪是空间太阳望远镜1m光学系统达到0.1“分辨率关键之一。介绍了基于FPGA实现SST相关算法的方法,如2×2矢量基蝶形FFT、模块化结构、两级状态机、动态块浮点、并行流水时序等.20MHz下32×32图像相关算法在XCV800芯片上实现仅713 微秒,像元拟合精度优于1/50.

2021-03-11 16:07

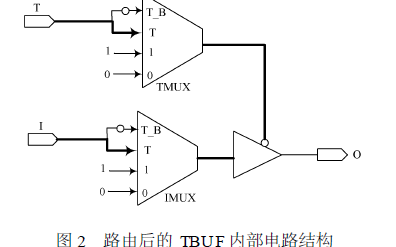

FPGA 动态局部可重构技术中基于三态缓冲器( Tri2state Buffer ,TBUF) 总线宏结构的基础上,采用Xilinx ISE FPGA Editor 可视化的方法实现总线宏的设计,并借助可重构硬件平台———XCV800 验证板,通过设计动态可重构实验,论证总线宏设计的正确性。

2018-12-14 14:27

IC FPGA 98 I/O 144TQFP

2023-04-06 16:00

IC FPGA 94 I/O 144CSBGA

2023-04-06 16:00

IC FPGA 166 I/O 240PQFP

2023-04-06 16:00

IC FPGA 94 I/O 144CSBGA

2023-04-06 16:00

IC FPGA 94 I/O 144CSBGA

2023-04-06 16:00