什么是Logic Synthesis?Logic Synthesis用于将输入的高级语言描述(如HDL、verilog)转换为门级电路的网络表示。

2023-10-24 15:56

Xilinx公司讲述:Getting Started with Vivado High-Level Synthesis

2018-06-04 13:47

全局综合(Global Synthesis)全局综合意味着整个设计在一个Synthesis Design Run流程中完成,这样会带来几个好处。

2022-07-15 11:39

教您如使用PlanAhead 13.1进行设计应用,通过一个设计程序,来体验PlanAhead的功能强大

2018-06-05 09:46

Vivado IPI (IP Integrator)提供了直观的模块化的设计方法。用户可以将Vivado IP Catalog中的IP、用户自己的RTL代码、或者用户已有的BD文件添加到IP Integrator中构成Block Design,设计更复杂的系统,如下图所示。

2022-07-15 11:39

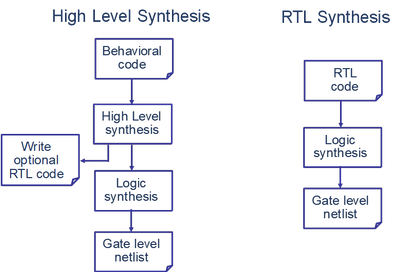

说起高层次综合技术(High-level synthesis)的概念,现在有很多初学者简单地把它理解为可以自动把c/c++之类地高级语言直接转换成底层硬件描述语言(RTL)的技术。其实更准确的表述是:由更高抽象度的行为描述生产电路的技术。

2022-02-08 17:26

是创建并定制 IP,生成这些 IP 的 output product (包括 IP 的 dcp);然后把第三方生成的网表文件和 IP XCI 的相关文件都加到 Vivado 的 post-synthesis 工程中。

2023-06-08 15:43

在FPGA设计里,设计仿真完成RTL代码设计后便是交给设计套件进行综合及布局布线。在综合过程里,Vivado里提供的参数选项有点儿多,今天闲暇抽空梳理下。 -flatten_hierarchy 该参数提供三个可选项: full:将我们整个设计层次打平,只保留顶层设计,对模块间进行边界优化(可以理解为我们整个设计被塞到一个Module里)。 none:完全保留设计原始层次,不执行任何边界优化。该选项工具进行的优化最少,消耗的资源最多,层次保留最完整。 rebuild:在进行综

2021-06-01 11:20

在上一章HLS的端口综合里有提及,HLS综合后的端口分为2中类型:BlockLevel和Port Level Interface。其中Port level是我们需要重点关注的,它又可以细分为4中类型: A. AXI4-Interface:支持Stream,Lite,Full共3中类型 B. NO I/O协议:无端口协议 C. Wire Handshakes:握手协议 D. Memory Interface:内存访问型的端口协议 接下来的几章,我们重点介绍下AXI接口类型如何在HLS中实现,首先看Lite端口: AXI-Lite端口的实现 使用Vivado HLS的AXI-Lite端口,可以实现: 把多个port打包到一组AXI-

2017-02-08 03:27

SystemVerilog 接口的开发旨在让设计中层级之间的连接变得更加轻松容易。 您可以把这类接口看作是多个模块共有的引脚集合。与必须在每个模块上定义多个引脚不同的是,您只需在接口中对引脚定义一次,之后只需在模块上定义接口即可。 如果稍后接口中涉及的信号被更改,则仅需更改接口即可。

2019-03-30 09:36