从上篇文章,我们可以很明显的看出STA的两大因素,一个是延迟计算,一个是约束检查。

2023-07-05 15:04

一、前言 无论是FPGA应用开发还是数字IC设计,时序约束和静态时序分析(STA)都是十分重要的设计环节。在FPGA设计中,可以在综合后和实现后进行STA来查看设计是否能满足时序上的要求。

2021-08-10 09:33

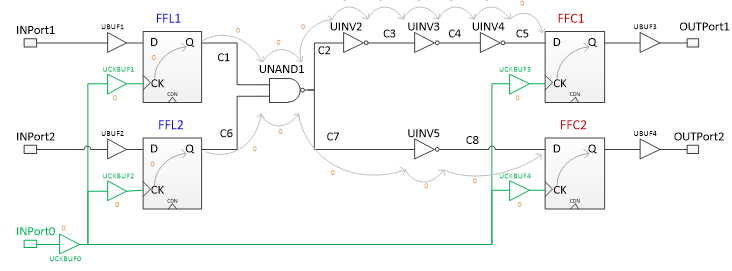

STA的准备工作包括:设定时钟、指定IO时序特性、指定false path和multicycle path

2023-05-26 17:20

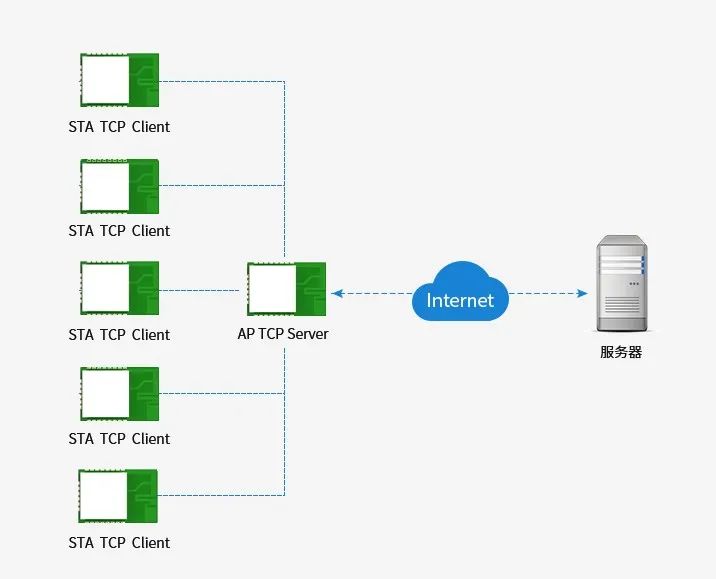

WiFi模块作为现代无线通信的核心组件,其工作模式直接决定了设备的联网能力和应用场景。AP(AccessPoint)、STA(Station)和AP+STA(混合模式)是三种最常见的工作模式,它们

2025-03-27 19:33 亿佰特物联网应用专家 企业号

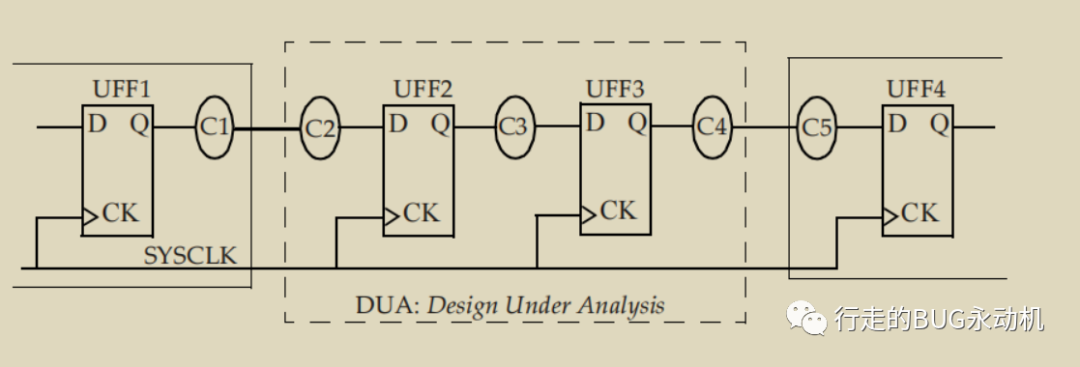

静态时序分析(STA)是用来分析数字电路是否满足时序目标的技术手段之一。比如,检查CPU电路是否达到1GHz的目标频率。

2023-07-05 15:01

STA同步热分析仪是将热重分析仪TG与差示扫描量热仪DSC或差热分析仪DTA结合一体,在同一次测量中利用同一个样品,可同时得到质量变化和吸放热变化等信息,大大提高了实验的效率,因此,被广泛应用在很多

2023-08-15 10:54

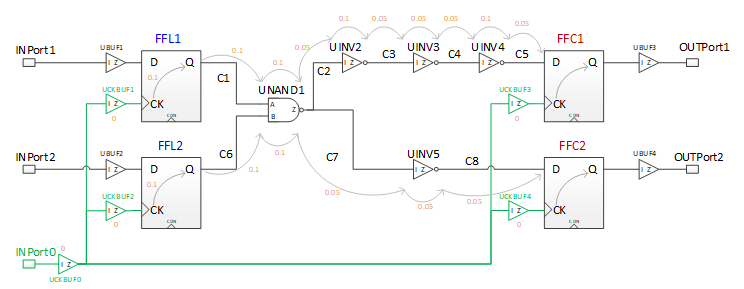

静态时序分析(Static Timing Analysis, 以下统一简称 **STA** )是验证数字集成电路时序是否合格的一种方法,其中需要进行大量的数字计算,需要依靠工具进行,但是我们必须了解其中的原理。

2023-06-27 11:43

什么是ANSI (American National Standard Institite) 英文缩写: ANSI (American National Standard Institite) 中文译名: 美国国家标准协会

2010-02-22 10:04

时序约束的目的就是告诉工具当前的时序状态,以让工具尽量优化时序并给出详细的分析报告。一般在行为仿真后、综合前即创建基本的时序约束。Vivado使用SDC基础上的XDC脚本以文本形式约束。以下讨论如何进行最基本时序约束相关脚本。

2022-03-11 14:39

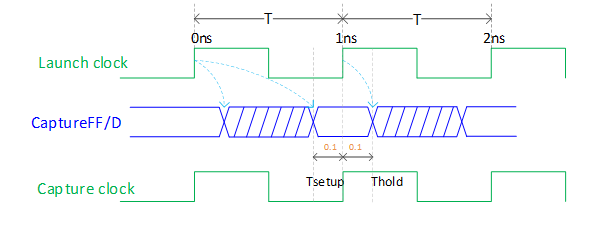

Setup时间是,为了寄存器可靠的采样到数据,数据必须提前于采样时钟沿稳定的最小时间。

2023-07-05 15:07