本文可让开发者们看懂 AMD Vivado Design Tool 2023.2 中的“AMD Versal Adaptive SoC CPM PCIE PIO EP 设计”CED 示例。

2024-05-10 09:39

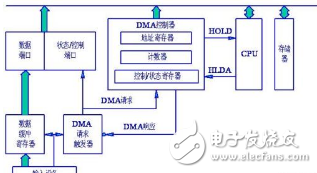

总线上的数据的传递有两种形式。一种为程控输入/输出(PIO)另一种为直接存储器访问(DMA)。

2018-01-24 10:48

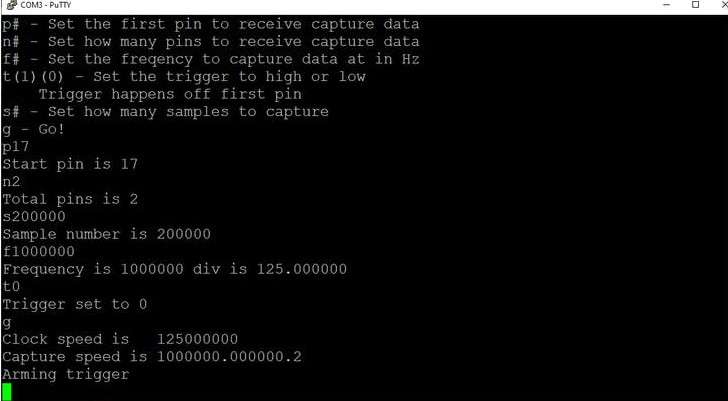

基于RP2040的Pico可用作PIO的逻辑分析仪。扩展示例以将结果导出到sigrock和PulseView。

2021-04-27 15:08

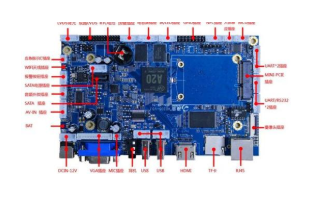

集成ALC662声道,板载功放 内建1*NGFF-A扩展槽,支持Wifi/蓝牙内建1*NGFF-B(for SSD),1*SATA支持4*USB 3.0,5*USB 2.0

2019-10-22 10:44

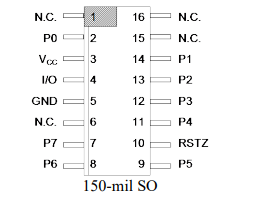

DS28E04-100是具有7个地址输入的4096位,1-Wire® EEPROM芯片。地址输入直接映射到1-Wire 64位器件ID号上,使主机系统能够在多器件1-Wire网络环境中直接识别出DS28E04-100的物理地置和功能。4096位EEPROM阵列配置为16页,每页32字节,另外还有用来进行写操作的32字节暂存器。EEPROM存储器页可单独进行写保护或置为EPROM仿真模式,此时每一位只能由1变为0。除存储器外,DS28E04-100还具有两个通用I/O端口,可用于输入或产生电平和/或脉冲输出。状态变化寄存器还用于指示端口状态变化。DS28E04-100通过单触点1-Wire总线进行通信。通信符合标准的Dallas Semiconductor 1-Wire协议。

2025-02-26 15:29

DS2408是一款8通道、可编程I/O 1-Wire® IC。PIO输出可配置为开漏结构,具有100Ω的最大导通电阻。稳固的PIO通道访问通信协议确保PIO输出设置变化没有误差。数据有效选通输出,可用来锁存

2025-02-26 16:12

GX2413是双通道可编程I / O 1-Wire芯片。 PIO输出配置为开漏,提供高达20mA的连续吸收能力和高达28V的关断状态工作电压。 使用专用的设备级命令协议来执行PIO PIN的控制和感

2023-12-07 09:40

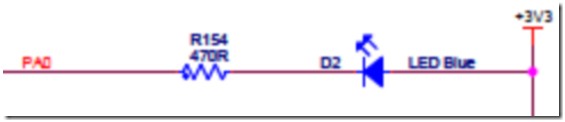

对单片机的操作需要通过对相关寄存器的访问来实现。比如,为调节PA0引脚上的电平,首先我们需要允许PIOA控制PA0引脚。通过查看寄存器说明可知,这只要向相应的PIO使能寄存器(PIO_PER)写入0x01就可以了。同时,也可以查到PIOA的

2018-12-11 16:12

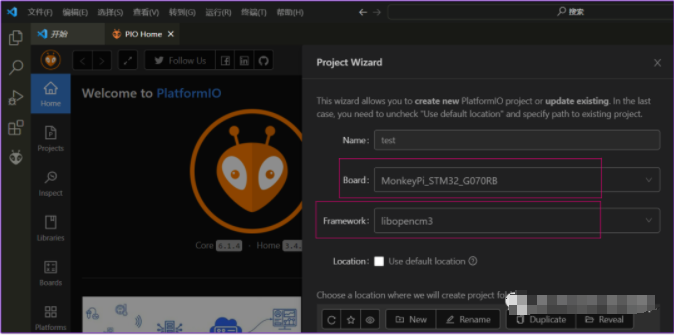

使用Platformio平台的libopencm3开发框架来开发STM32G0,开发环境为VSCode+PIO插件,这里以开发STM32G070RB芯片为例介绍。

2023-01-17 10:56

指纹识别模块的硬件设计采用 SOPC的设计思路[1],在FPGA内部实现指纹读取 UART接口、FLASH存储器接口、SDRAM控制器、PIO控制的键盘和 LCD显示接口。

2018-08-18 09:45