FPGA 芯片通过 I2C 总线连接 EEPROM 24LC04, I2C 的两根总线各上拉一个 4.7K的电阻到 3.3V,所以当总线上没有输出时会被拉高, 24LC04 的写保护没有使能,丌然 FPGA 会无法写入数据。因为在电路上 A0~A2 都为低,所以 24LC04 的设备地址为 0xA0。PGL12G 板子,是将FPGA芯片作为IIC 主站设备,将EEPROM作为了个从站设备; 原理图: I2C 设备的操作可分为写单个存储字节,写多个存储字节,读单个存储字节和读多个存储字节。 ①总线空闲状态 I2C 总线总线的 SDA 和 SCL 两条信号

2020-11-26 14:30

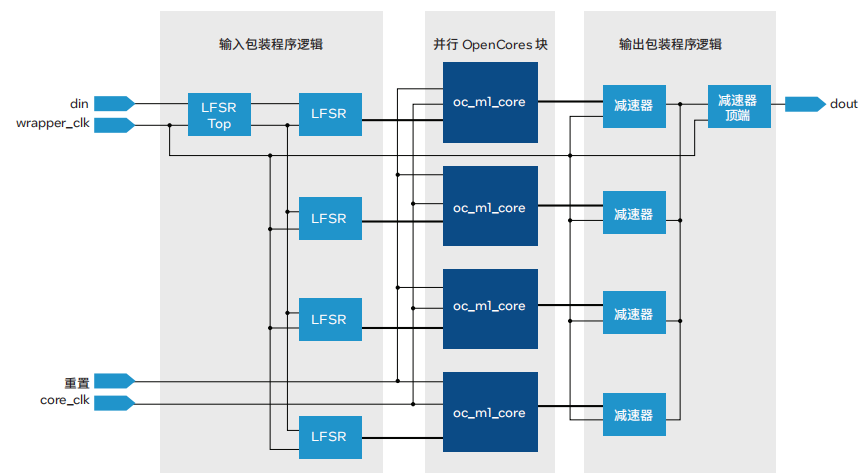

AEMB软核处理器设计的SoC系统验证平台 本文采用OpenCores组织所发布的32位微处理器AEMB作为SoC系统的控制中心,通过Wishbone总线互联规范将OpenCores组织

2010-05-24 11:02

Opencores是一个开源的数字电路设计社区,它提供了免费的开源IP(知识产权)核心,让工程师和爱好者们可以使用这些IP核心来构建自己的数字电路设计。Opencores的IP核心包括处理器、总线接口、视频、音频和其他数字电路组件

2023-04-03 10:39

与同类FPGA相比,Agilex 7 FPGA可为OpenCores公开发布的设计提供超过一个速度等级的内核性能提升。

2024-08-30 17:07

一直想做一个可以供大家学习、使用的开源IP库,类似OpenCores,OC上IP在领域内的IP很少,通用性强一点,所以作为OC的“补充”,所以做了一个开源IP库,

2023-05-06 09:16

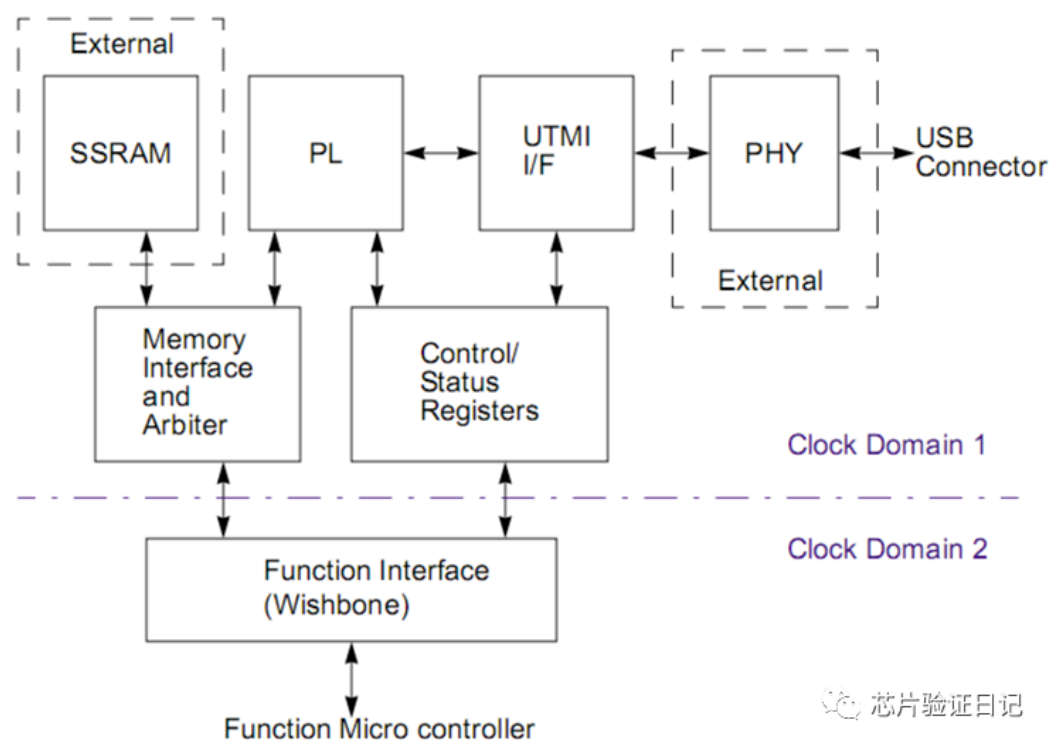

。今天是开篇,先分享一个高质量的usb2.0项目给大家。 本文通过集成各个小项目,最后形成USB这个综合项目,分享给对USB感兴趣的朋友。废话不多说,直接上干货。 1. USB2.0的IP核 本项目的核心来自opencores,具体的网址是:https://opencor

2022-11-20 22:53

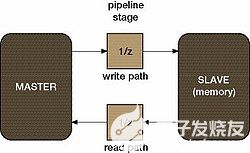

大规模FPGA/ASIC SoC设计的设计和开发迫使设计人员实现具有标准化模块接口的模块化架构,该接口以任何可能的配置连接各种IP模块。OpenCores发布了最流行的互连架构之一,称为

2022-11-14 15:38

OpenCores网站提供的OC8051 IP核与8051的系统结构相同,如图1所示。该IP核兼容所有8051指令系统,内部资源包括:8位CPU,寻址能力达2×64K;4 KB的ROM和128字节

2020-09-28 23:35