AXI接口虽然经常使用,很多同学可能并不清楚Vivado里面也集成了AXI的Verification IP,可以当做AXI的master、pass through和slave,本次内容我们看下

2023-07-27 09:19

依据SPI同步串行接口的通信协议, 设计一个可配置的、高度灵活的SPI Master 模块,以满足正常、异常及强度测试要求。利用Verilog 语言实现SPI接口的设计原理和编程思想。

2018-11-05 17:42

A Memory Write Request of 1 DW with no bytes enabled, 即Memory Write 类型tlp中只有1DW的data,且length字段为1,并且tlp header中的First DW BE[3:0] 和Last DW BE[3:0]均为0。

2023-05-15 14:24

为了让 Linux 节点的 iptables 能够正确查看桥接流量,请确认 sysctl 配置中的 net.bridge.bridge-nf-call-iptables 设置为 1。例如:

2022-08-26 10:46

EtherCAT是一种实时工业以太网技术,其CAT为Control Automation Technology即控。

2023-05-12 17:12

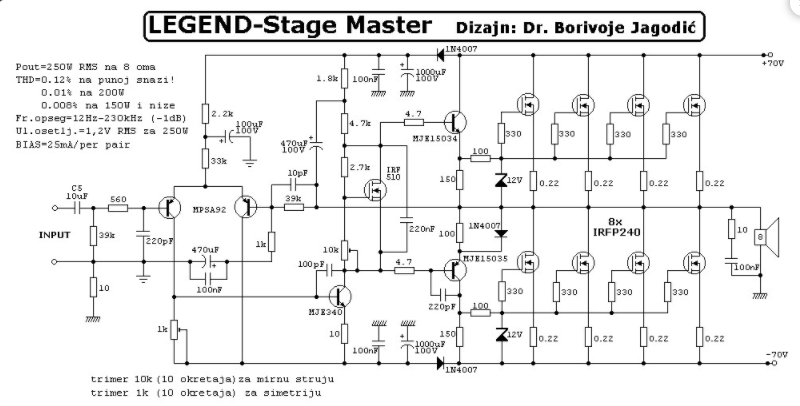

这是称为Legend-StageMaster的250WRMS功率放大器电路。这是Legend-StageMasterMK2的旧版本。该电路基于功率MOSFET,为室内音响系统提供了出色的输出性能。

2022-05-30 17:27

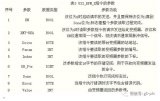

初始化指令USS-INIT用于允许或禁止PLC和变频器之间的通讯,在执行其他USS协议前,必须先成功的执行一次USS-INIT指令,只有当该指令成滚执行完成后其完成位(DONE)置位后,才能继续执行下面的指令。次USS-INIT指令的参数如表1所示:

2018-09-13 17:08

如果设备的IP地址与PG/PC的网卡的IP地址不在同一子网内,必须先给网卡分配额外的IP地址,这个IP地址需要与设备的子网地址相同。

2024-02-25 11:07

FPGA 芯片通过 I2C 总线连接 EEPROM 24LC04, I2C 的两根总线各上拉一个 4.7K的电阻到 3.3V,所以当总线上没有输出时会被拉高, 24LC04 的写保护没有使能,丌然 FPGA 会无法写入数据。因为在电路上 A0~A2 都为低,所以 24LC04 的设备地址为 0xA0。PGL12G 板子,是将FPGA芯片作为IIC 主站设备,将EEPROM作为了个从站设备; 原理图: I2C 设备的操作可分为写单个存储字节,写多个存储字节,读单个存储字节和读多个存储字节。 ①总线空闲状态 I2C 总线总线的 SDA 和 SCL 两条信号

2020-11-26 14:30