基于FPGA的嵌入式应用在近几年来作为一个比较新颖的课题,本文在研究各种核间通信机制的基础上,提出了一种基于Mailbox核间机制的多核处理系统,在该系统中集成了Xilinx的软核处理器Microblaze,其降低了使用多信号处理板但来的成本问题同时还节省了空间,对更好的发挥多核系统提出了新的解决方案。

2017-11-22 17:31

目前很多芯片都会有几个core核,有的是Cortex M0+、M4、M7、A53、A73等等,有的有着2核、3核、4核甚至6核8核,不同的核的主频支持度不一样,适用的具体应用场景也不同,因此需要IPC(Inter-processor communication)来核间通信,进行数据的交互。

2023-09-05 17:29

现在业界的许多解决方案都包含多个处理器,或者是硬核处理器,如Arm A9、A53或R5,软核如MicroBlaze、Arm Cortex-M1/M3,或者是两者的组合。

2023-09-21 15:23

在scmi协议初始化的时候,scmi_reset_register会注册0x16的回调函数,详细分析见2.2.1 SCMI reset协议初始化内容。在drivers/firmware/arm_scmi/reset.c中

2023-10-16 17:09

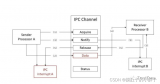

发送数据时,对数据进行IPH封装,根据前述的板卡地址映射表选择目的PCI地址,再调用总线接口函数完成数据传输。发送方通过写接收板卡桥芯片的mailbox寄存器,将传输地址及数据长度信息通知接收

2018-08-18 11:30

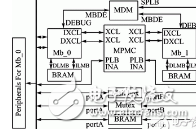

之间通过Mutex模块实现同步功能,通过Mailbox模块实现通信和中断功能,通过共享BRAM模块实现大块通信功能,并进行了有效的功能验证。该SOPC系统在XUPV5LX110T开发板上得到验证。测试结果表明,两软核处理器之间有效地实现了同步,通信和中断功能,达到了预期的效果,验证了方案的有效性。

2017-11-18 03:50