传输。 EDP接口概述 EDP接口是一种专为便携式设备设计的显示接口技术。与传统的DisplayPort接口相比,EDP接口具有更小的尺寸、更低的功耗和更高的集成度。它采用了一种名为“lane”的传输通道

2024-08-09 11:13

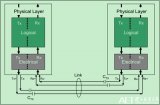

需要注意的是,PCIe总线采用的是嵌入式时钟,即只有数据Lane,并没有时钟Lane(具体在前面的文章中已经详细地介绍过了)。也就是说,以Gen1为例,虽然2.5GT/s使用的时钟为2.5GHz,但是从数据Lane上

2018-06-09 09:39

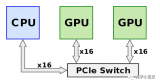

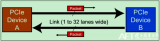

PCIe 1.0、2.0、3.0传输速率分别为2.5GHz、5GHz和8GHz,单lane带宽分别达到250MB/s、500MB/s和1GB/s。PCIe总线由不同lane连接,多个lane合在一起

2024-01-29 10:39

2014年,NVLink 1.0发布,并应用在P100芯片上,如下图所示。两颗GPU之间有4条NVlink, 每个link中包含8个lane, 每条lane的速率是20Gb/s, 因此整个系统的双向带宽为160GB/s,是PCIe3 x16带宽的5倍。

2023-10-11 15:32

进行了全连接,最后输出走这一条LSTM。第一规划Lane横向行为的分类情况,选择是否走此Lane,选择Lane1还是Lane2。第二是它的动力学,速度是什么样的,就是它

2018-07-16 10:54

当器件工程师选定一颗Camera模组或一款OLED屏的时候,硬件工程师就需要根据这颗器件的参数,来计算数据传输所需的带宽,以此确认用哪种协议、需要多少lane、以及平台是否支持。

2024-02-23 09:27

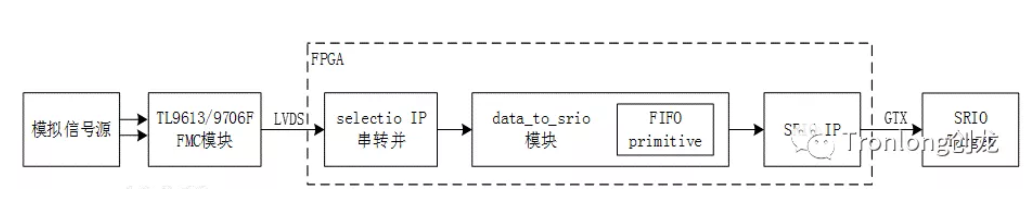

的地址空间,数据量为32KByte,使用SWRITE方式,期间每传16KByte数据后就发送一个DOORBELL信息,让C6678做乒乓处理。Kintex-7通过SRIO与C6678连接,共4个lane

2020-06-15 18:18

自动驾驶的技术发展速度一直很迅速,尤其是在过去的1-2年中,在较低的自动驾驶级别技术上已经实现了重大突破。车道偏离系统(Lane departure systems)的功能已经从仅发出警告发展到全主动的车道保持。

2020-01-28 17:50

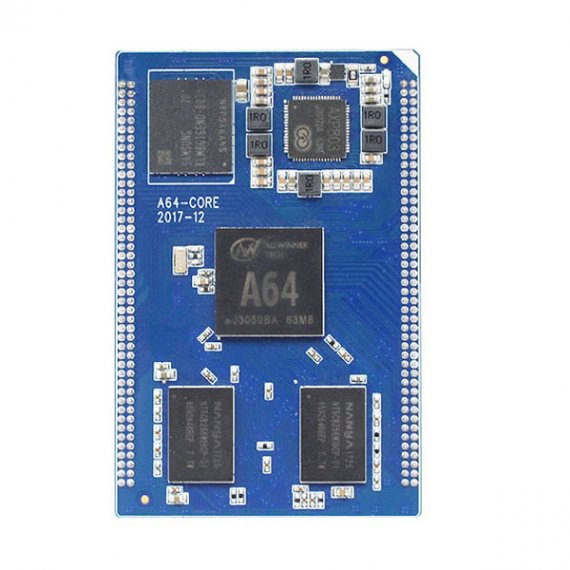

存储配置:1G DDR3(不能扩展) + 8G eMMC(可扩展16G和32G)。 显示能力:HDMI 1080P、单8LVDS 1366*768、4-lane MIPI 1920x1200。

2019-11-11 11:46

除了差分总线,PCIe还引入了嵌入式时钟的技术(Embedded Clock),即发送端不再向接收端发送时钟,但是接收端可以通过8b/10b的编码从数据Lane中恢复出时钟。

2018-04-19 09:20