MediaTek今日宣布,其ASIC服务将扩展至112G远程(LR)SerDes IP芯片。MediaTek的112G 远程 SerDes采用经过硅验证的7nm FinFET制程工艺,使数据中心能够快速有效地处理大量特定类型的数据,从而提升计算速度。

2019-11-12 14:22

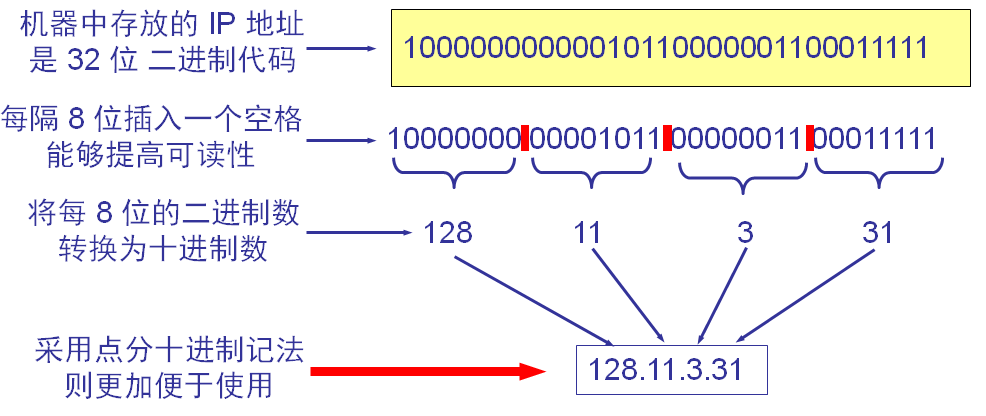

IP协议(Internet Protocol),又称之为网际协议,IP协议处于IP层工作,它是整个TCP/IP协议栈的核心协议之一,上层协议都要依赖

2023-02-14 10:14

动态IP和静态IP的区别在于:动态IP需要在连接网络时自动获取IP地址以供用户正常上网,而静态IP是ISP在装机时分配给

2017-12-27 11:14

介绍如何设计HLS IP,并且在IP Integrator中使用它来作一个设计——这里生成两个HLS blocks的IP,并且在一个FFT(Xilinx IP)的设计中

2017-02-07 17:59

在FPGA实际的开发中,官方提供的IP并不是适用于所有的情况,需要根据实际修改,或者是在自己设计的IP时,需要再次调用时,我们可以将之前的设计封装成自定义IP,然后在之后的设计中继续使用此

2022-04-21 08:58

在近期的博文《新思科技率先推出PCIe 7.0 IP解决方案,加速HPC和AI等万亿参数领域的芯片设计》中,新思科技宣布推出综合全面的PCIe Express Gen 7(PCIe 7.0)验证IP(VIP)解决方案

2024-07-24 10:11

Vivado Design Suite 可提供围绕 IP 的设计流程,支持您将来自各种设计的 IP 模块添加到自己的设计中。此环境的核心是可扩展的 IP 目录,其中包含 AMD 赛灵思提供的即插即用

2022-10-26 09:23

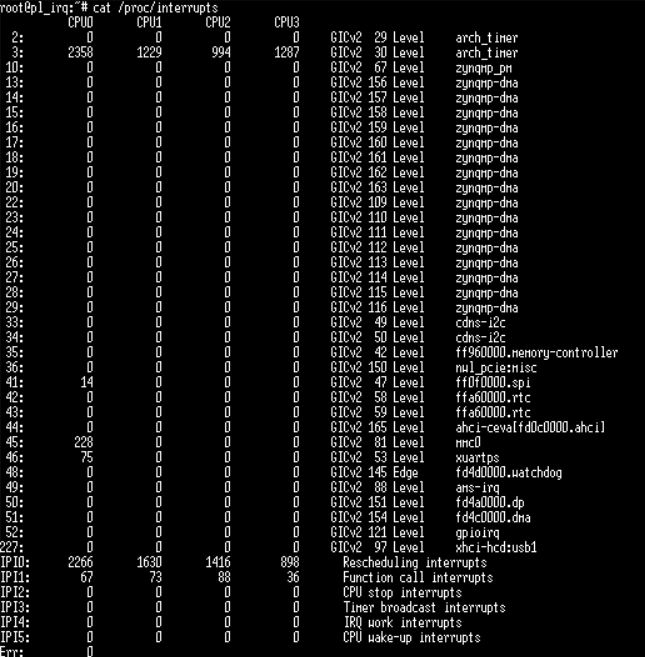

有时我们需要为官方 IP 或者自己创建的 IP 生成 kernel module,然后在 linux kernel space 里使用 kernel module 来控制这个 IP。如果要使用

2022-08-02 11:35

学完SDRAM控制器后,可以感受到SDRAM的控制器的书写是十分麻烦的,因此在xilinx一些FPGA芯片内已经集成了相应的IP核来控制这些SDRAM,所以熟悉此类IP核的调取和使用是非常必要的。下面我们以A7的DD

2019-11-10 10:28