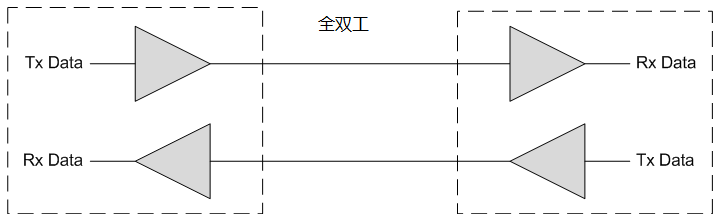

典型的全双工(Full Duplex)系统如下图所示,芯片1和芯片2之间有彼此独立的数据传输线,这意味着芯片1和芯片2可以同时给对方发送数据而不会发生冲突。SPI/UART采用的就是全双工通信方式。半双工系统则不同,芯片1和芯片2之间只有一条专用的且被彼此共享的数据传输线。这就要求芯片1和芯片2必须协商好,当前谁发送数据,谁接收数据。如果两者同时发送数据就会导致发送冲突,从而造成数据丢失。I2C采用的就是半双工通信方式。

2024-09-18 10:39

OLOGIC块在FPGA内的位置紧挨着IOB,其作用是FPGA通过IOB发送数据到器件外部的专用同步块。

2019-02-17 10:55

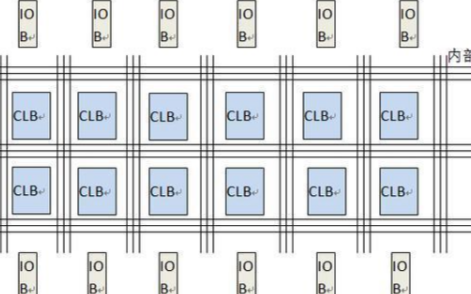

FPGA(现场可编程门阵列)的架构主要由可配置逻辑模块(CLB)、输入/输出模块(IOB)以及可编程互连资源组成。

2024-03-14 17:05

OLOGIC 资源 OLOGIC块在FPGA内的位置紧挨着IOB,其作用是FPGA通过IOB发送数据到器件外部的专用同步块。OLOGIC 资源的类型有OLOGIC2(位于HP I/O banks

2018-04-25 16:50

FPGA采用了逻辑单元阵列LCA这样一个概念,内部包括可配置逻辑模块CLB、输出输入模块IOB和内部连线三个部分。

2017-05-17 16:35

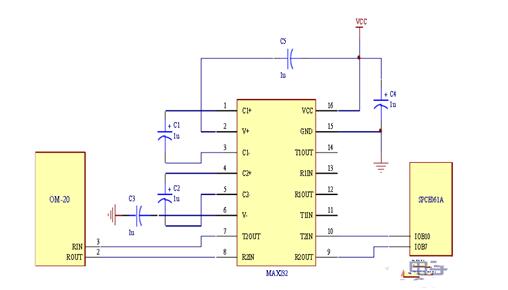

SPCE061A单片机通过串行口与指纹识别模块OM—20通信。SPCE061A单片机内部有一个标准全双工的通用异步接收器/发送器UART。UART的接收信号Rx和发送信号Tx分别与IOB7和IOB10共用,属于B口的特殊功能。

2019-09-22 11:08

FPGA主要由大量的CLB来作为最小逻辑单元,使用内部连线将这些最小的逻辑单元连接,完成更大的逻辑功能单元,再与这些IOB连接完成最终结果或信号的输入输出。

2019-07-12 15:24

FPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个概念,内部包括可配置逻辑模块CLB(Configurable Logic Block)、输出输入模块IOB(Input Output Block)和内部连线(Interconnect)三个部分。

2019-06-27 17:52

Virtex-6每个I/O片(I/O Tile)包含两个IOB、两个ILOGIC、两个OLOGIC 和两个IODELAY,如图5-24 所示。

2017-02-11 09:21

可编程逻辑块(CLB)和输入输出模块(IOB)。CLB是实现逻辑功能的基本单元,主要由逻辑函数发生器、触发器、数据选择器等数字逻辑电路构成。IOB则提供了芯片引脚和内部逻辑阵列之间的连接,可独立编程为输入、输出和双向I/O。

2024-03-27 14:48