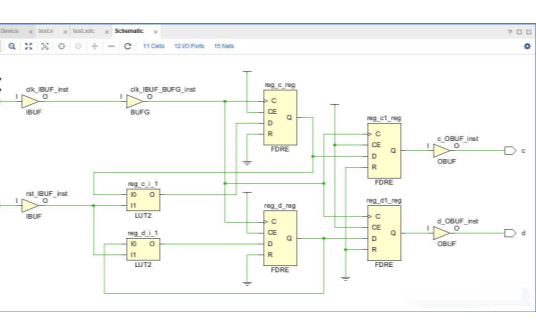

xilinx FPGA的资源一般指IOB,CLB,BRAM,DCM,DSP五种资源。其中IOB就是input/output block,完成不同电气特性下对输入输出信号的的驱动和匹配要求。

2020-12-29 16:59

FPGA基础资源之IOB的应用 1.应用背景 在我们做时序约束时,有时候需要对FPGA驱动的外围器件进行input_delay/output_delay进行约束。不知道,大家有没有被以下这种

2022-12-25 16:30

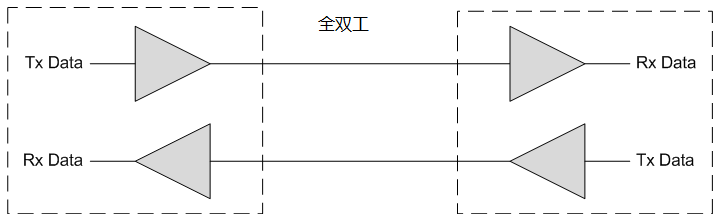

典型的全双工(Full Duplex)系统如下图所示,芯片1和芯片2之间有彼此独立的数据传输线,这意味着芯片1和芯片2可以同时给对方发送数据而不会发生冲突。SPI/UART采用的就是全双工通信方式。半双工系统则不同,芯片1和芯片2之间只有一条专用的且被彼此共享的数据传输线。这就要求芯片1和芯片2必须协商好,当前谁发送数据,谁接收数据。如果两者同时发送数据就会导致发送冲突,从而造成数据丢失。I2C采用的就是半双工通信方式。

2024-09-18 10:39

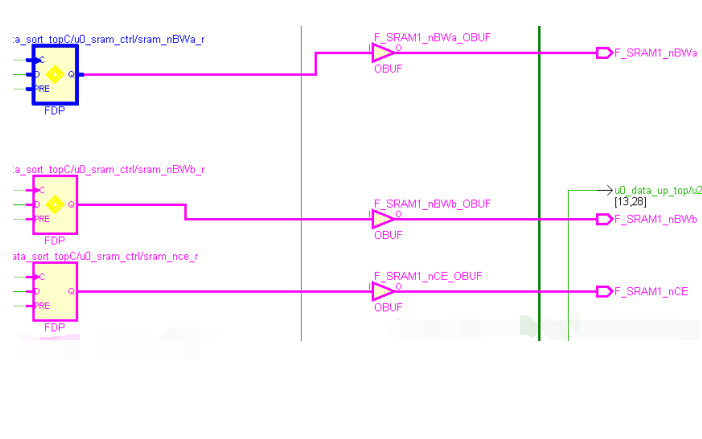

一个fpga主要是由可编程输入输出单元(图中的IOB模块),可编程逻辑单元(CLB模块),块RAM(图中的BRAM,也属于内嵌硬件),数字时钟管理(DCM,也属于内嵌硬件),还有一些内嵌的专用的硬件模块(DSP),IOB寄存器就在图中的

2020-12-28 17:13

CLB和IOB是边界单元吗?最好的祝福,迈克尔

2020-04-14 09:37

一个fpga主要是由可编程输入输出单元(图中的IOB模块),可编程逻辑单元(CLB模块),块RAM(图中的BRAM,也属于内嵌硬件),数字时钟管理(DCM,也属于内嵌硬件),还有一些内嵌的专用的硬件模块(DSP),IOB寄存器就在图中的

2020-12-28 17:13

xilinx FPGA IOB约束使用以及注意事项 一、什么是IOB约束 在xilinx FPGA中,IOB是位于IO附近的寄存器,是FPGA上距离IO最近的寄存器,同时位置固定。当你输入或者输出

2025-01-16 11:02

关于IOB寄存器的使用,网上已经有很多资料可以查找,这里就不多余说了。

2020-12-28 17:13

嗨,我的项目合成确定,但在奇怪的错误实现中断:地点:1012- 已发现时钟IOB / DCM组件对未放置在最佳时钟IOB / DCM站点对。时钟组件放置在现场。如果将时钟IO / DCM站点放置

2019-05-10 09:29

=“E32”;时钟从外部输入到系统中。当我运行编译到“地图”部分有一个错误发生如下:警告:放置:1154 - 已发现时钟IOB / BUFGCTRL时钟组件对未放置在最佳时钟IOB / BUFGCTRL站点

2019-09-06 10:33